【導(dǎo)讀】前面小編為大家講解了如何調(diào)整PCB布局以降低超級結(jié)MOSFET輻射,從而來提高效率。這里將接著為大家講解為什么使用超級結(jié)MOSFET時柵極會發(fā)生振蕩?有什么好的方法解決?如果調(diào)整PCB布局,該怎么去調(diào)整?

本文接著上一篇:《如何調(diào)整PCB布局?降低超級結(jié)MOSFET輻射、提高效率》,繼續(xù)講解為什么使用超級結(jié)MOSFET時柵極會發(fā)生振蕩?

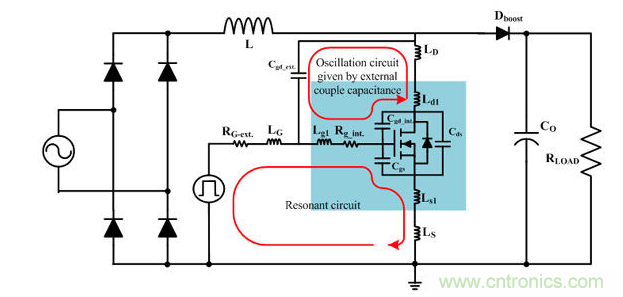

因為MOSFET是單極性器件,因此寄生電容是開關(guān)瞬態(tài)唯一的限制因素。電荷平衡原理降低了特定面積的導(dǎo)通電阻,而且,與標(biāo)準(zhǔn)MOSFET技術(shù)相比,相同RDS(ON)下的芯片尺寸更小。圖1顯示超級結(jié)MOSFET和標(biāo)準(zhǔn)平面型MOSFET的電容。標(biāo)準(zhǔn)MOSFET的Coss為中度線性變化關(guān)系,而超級結(jié)MOSFET的Coss曲線呈現(xiàn)高度非線性關(guān)系。因為單元密度較高,超級結(jié)MOSFET的Coss初始值較高,但超級結(jié)MOSFET中,在約50V漏源電壓附近,Coss會迅速下降,如圖1所示。當(dāng)使用超級結(jié)MOSFET應(yīng)用到PFC或DC/DC轉(zhuǎn)換器時,這些非線性效應(yīng)可能造成電壓和電流振蕩。圖2顯示簡化的PFC電路示意圖,包括功率MOSFET內(nèi)部寄生元件和外部振蕩電路,外部振蕩電路包含由布板帶來的外部耦合電容Cgd_ext.)。

圖1. 平面型MOSFET和超級結(jié)MOSFET輸出電容的比較

一般來說,有多個振蕩電路會影響MOSFET的開關(guān)特性,包括內(nèi)部和外部振蕩電路。 在圖2的PFC電路中,L、Co和Dboost分別是電感、輸出電容和升壓二極管。Cgs、Cgd_int和Cds是功率MOSFET的寄生電容。Ld1、Ls1和Lg1是功率MOSFET的漏極、源極和柵極邦定線以及引腳電感。Rg_int和Rg_ext是功率MOSFET的內(nèi)部柵極電阻和電路的外部柵極驅(qū)動電阻。Cgd_ext是電路的寄生柵極-漏極電容。LD、LS和LG是印刷電路板(PCB)的漏極、源極和柵極走線雜散電感。當(dāng)MOSFET打開或關(guān)閉時,柵極寄生振蕩通過柵極-漏極電容Cgd和柵極引線電感Lg1在諧振電路內(nèi)發(fā)生。

圖2.包含功率MOSFET內(nèi)外部寄生元件的PFC電路簡圖

在諧振條件(ωL = 1/ωC)下,柵極和源極 電壓中生成的震蕩電壓遠(yuǎn)大于驅(qū)動電壓。因諧振變化而產(chǎn)生的電壓振蕩與品質(zhì)因數(shù)成正比, Q(=ωL/R = 1/ωCR)。當(dāng)MOSFET關(guān)閉時,漏極寄生電感(LD + Ld1)、柵極-漏極電容Cgd和柵極引線電感Lg1網(wǎng)絡(luò)造成柵極 振蕩電壓。如果柵極電阻 (RG-ext.+Rg_int.)極小,則Q變大。另外,LS兩端的壓降和Ls1源極雜散電感在柵極-源極電壓中產(chǎn)生振蕩,可用表達(dá)式(1)表示。寄生振蕩可能造成柵源極擊穿、不良EMI、較大開關(guān)損耗、柵極控制失效,甚至可能造成MOSFET故障。

優(yōu)化電路設(shè)計,最大限度地提高超級結(jié)MOSFET的性能而又不產(chǎn)生負(fù)面影響非常重要。

相關(guān)閱讀: