【導讀】基于可編程門陣列FPGA的核心技術實現(xiàn)航空電子系統(tǒng)的設計,提高了集成度,降低功耗,減小體積,提高平均間隔時間,降低設計風險,MIL-STD-1553 的市場隨著這項技術的實現(xiàn)也變得繁榮起來。MIL-STD-1553 核心的種種優(yōu)勢,使 ASIC 傳統(tǒng)徹底退出歷史舞臺。FPGA 核心技術如同強心劑,賦予系統(tǒng)不同的特性,給 MIL-STD-1553 的設計帶來了諸多優(yōu)勢。

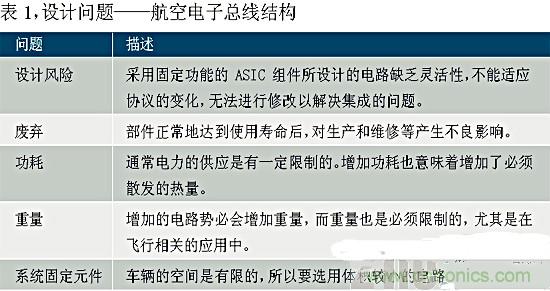

一、系統(tǒng)設計面臨的問題

由于競爭的壓力和對最佳戰(zhàn)斗性能無止境的追求,軍用航空電子從簡單、獨立的設備發(fā)展到如今以每秒百萬位乃至更快的速度交換信息的高級智能系統(tǒng)網(wǎng)絡。這也帶來了必須克服的許多設計問題。

在要求高性能的軍用設計中,每項設計都要減少空間、功耗和重量,滿足這些要求至關重要。這項要求直接作用于芯片級別,單一芯片體積減小后對所需板卡的要 求也會降低,從而降低了對封裝外殼、固定元件、冷卻器件甚至是電源的要求。同樣,每多增加一個組件,都會增加一些引發(fā)故障的機會。減少芯片數(shù)量的設計必然 有助于緩解這些問題。

廢棄則是像 MIL-STD-1553 設計實施這類長期項目所面臨的另一個問題。每個組件無論其是由世界最大的制造商提供,還是來自于產(chǎn)量較小的專業(yè)供應商,都存在著廢棄的風險。單一來源的組 件不但面臨著被廢棄的風險,還有個長期價格保護的問題,特別是那些從原有項目繼承的設計,這個問題更為明顯。對于已經(jīng)部署的系統(tǒng),由于所涉及的代價過高, 應盡量避免由于廢棄組件而重新對系統(tǒng)進行驗證。

當系統(tǒng)架構(gòu)師指定一種系統(tǒng)設計時,必然會存在架構(gòu)無法正確實現(xiàn)的某種風險。一個非常典型的問題是:經(jīng)常在設計過程中或架構(gòu)確定很久之后(如在集成階段),才知道需求有所變化。這些變化一般都會增加對架構(gòu)的要求,并提出一些關于設計的常見問題,如:設計足夠靈活嗎?能提供充分的處理能力嗎?功能在硬件和軟件之間是否得以有效且高效地進行了區(qū)分?能達到關鍵時間要求嗎?

理想狀況下,所選定的架構(gòu)應功能強大、應用靈活,足以在初始部署階段就將風險降到最低,并且提供了一個允許系統(tǒng)隨著時間發(fā)展的平臺。

理想條件下,一個 MIL-STD-1553 設計師可以采用傳統(tǒng)的技術,使用有多個來源的 COTS 組件來解決這些問題。這種由大量市場提供的組件在性價比上有明顯的優(yōu)勢。

二、MIL-STD-1553 簡介

MIL-STD-1553 是一種定義數(shù)據(jù)總線的電子和協(xié)議特點的軍用標準。作為一種在軍用和商用領域廣泛應用超過 25 年之久的總線,并且符合 MIL-STD-1553 標準,它能以1Mbit/s的速率高度精確、極為可靠地傳輸數(shù)據(jù)。

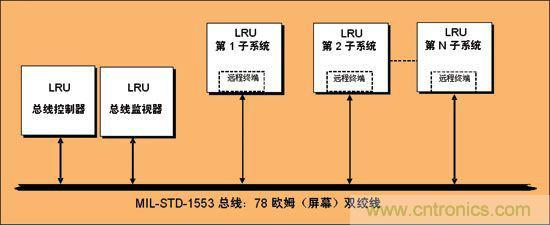

圖1: MIL-STD-1553 總線結(jié)構(gòu)

根據(jù) MIL-STD-1553 標準的規(guī)定,總線結(jié)構(gòu)由三個不同的硬件組成:

(1)總線控制器——總線控制器是總線上唯一允許在數(shù)據(jù)總線上發(fā)出命令,并負責引導數(shù)據(jù)總線中數(shù)據(jù)流的硬件設備。如果同時有幾個終端可以實現(xiàn)總線控制器的功能,同一時間內(nèi)只能有一個處于活動狀態(tài)。

(2)總線監(jiān)視器——總線監(jiān)視器是一個可以監(jiān)控總線上信息交換的終端。它可以用于飛行測試記錄、飛行故障診斷、維護記錄與任務分析,同 時還可作為一個備用總線控制器,它有足夠的信息可以接替總線控制器。然而,總線監(jiān)視器是一個被動的設備,它不能報告所傳輸信息的狀態(tài)。

(3)遠程終端——每個遠程終端都包括在數(shù)據(jù)總線和子系統(tǒng)間傳輸數(shù)據(jù)所必須的電子器件和支持性中間件。對于 MIL-STD-1553,子系統(tǒng)就是所傳輸數(shù)據(jù)的發(fā)送者和接收者。這些終端不能作為總線控制器或總線監(jiān)視器使用。

[page]

三、MIL-STD-1553 系統(tǒng)實施

像其它軍用網(wǎng)絡技術一樣,航空電子市場中的 MIL-STD-1553 測試和仿真實施也經(jīng)歷了從龐大的 DEC Unibus 卡到 19 英寸的通過機架安裝的組件,又發(fā)展到用于 VME 和 PCI 系統(tǒng)上的較小、較為集成的多通道背板,現(xiàn)在又出現(xiàn)了更小、集成度更高的 PCMCIA 接口。圖 2 描述了專用的 MIL-STD-1553 ASIC 芯片制造商的實施從離散的協(xié)議和收發(fā)器芯片組精簡到單一的體積小、功耗低的 ASIC 的發(fā)展過程。

圖2:ASIC發(fā)展過程

過去,典型的 MIL-STD-1553 系統(tǒng)一般都由多個COTS組件構(gòu)成,MIL-STD-1553 I/O通常由單一來源的帶有內(nèi)部處理功能的 ASIC 提供,這種內(nèi)部處理可提供消息處理與緩沖以及對 MIL-STD-1553 比特流進行編解碼等。ASIC 中可能含有也可能沒有向 MIL-STD-1553 總線提供物理接口的收發(fā)器組件。每個 ASIC 為一個雙冗余 MIL-STD-1553 通道提供此功能,所以支持多個 MIL-STD-1553 通道的系統(tǒng)就需要多個 ASIC 和收發(fā)器。與每個 MIL-STD-1553 總線的連接是通過板載變壓器實現(xiàn)的。最后,由一個或幾個可編程的 FPGA 設備將 MIL-STD-1553 ASIC 連接到主系統(tǒng),并提供更多的系統(tǒng)功能,如其它 I/O、存儲器訪問 和處理器接口等。

FPGA 有多種密度,通常以邏輯單元或門來度量。它們有多種形式架構(gòu),提供了豐富的 I/O 引腳可供使用。FPGA 還可提供內(nèi)部存貯器。例如,當前由Xilinx 推出的一流的 FPGA 存貯容量比三年前約增加了 10 倍。而且還提高了內(nèi)部速度,降低了成本?,F(xiàn)代 FPGA 海量的存貯和功能使其成為 MIL-STD-1553 設計最理想的選擇。其核心為預先定義的、且經(jīng)過測試的功能,這些功能可以應用到 FPGA 設計中。

促使工程師們?yōu)?MIL-STD-1553 實施選擇 IP 設計的原因有很多,其中包括:

廢棄部件管理——利用 IP 核心可以顯著地降低廢棄的風險。設計師不會束縛于某一個特定的部件、甚至是 FPGA 制造商。這與隨時可能會被放棄的單一來源的專用 MIL-STD-1553 協(xié)議 ASIC和處理器(及其制造方法)形成了鮮明的對比。對電路實施 FPGA后,設計可移植到最新的 FPGA 中,一般都無須改變其功能,減少了對軟件的修改(通常是項目中成本最大的部分)。

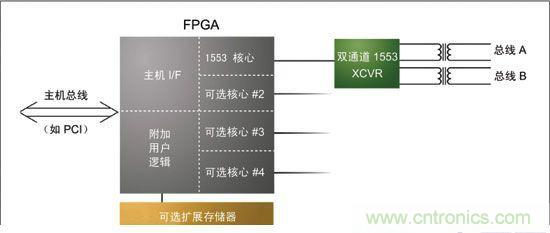

減小體積、提高可靠性、降低功耗和重量——將多種功能,包括處理器、I/O、MIL-STD-1553 和背板電路綜合到單一的IC中,可顯著地減少部件數(shù)量、板卡空間和熱負荷。這樣就增加了可靠性,進而提高了 MTBF。減少部件數(shù)量可以降低飛行設備系統(tǒng)對重量、空間及功耗的需求。如圖3所示,設計人員可以將多種功能綜合到單一的邏輯設備中,減少了部件的數(shù)量和體積。

圖3:邏輯設備

降低成本——由于實施了 FPGA 核心,生產(chǎn)和生命周期的成本會隨著時間而下降。FPGA 價格歷來是隨著項目的進行而顯著地下滑,而 ASIC 在長期的生產(chǎn)過程中價格卻會上漲。很多航空電子系統(tǒng)已經(jīng)在其設計中采用了 FPGA,一個 MIL-STD-1553 核心實例可以輕松地融入現(xiàn)有的芯片或同系列的其他更密集的芯片中。單一 FPGA 中集中了多通道實例可進一步節(jié)省成本,只因為單一 FPGA 內(nèi)可以容納多個通道接口。

便于重新編程——由 于支持對現(xiàn)場硬件的重新編程,核心的實施顯著降低了設計風險。如果系統(tǒng)需求發(fā)生變化,或者要修復一個錯誤時,基于 FPGA 的設計可以在軟件的控制下進行升級。這種靈活性還可以在硬件構(gòu)造完成后,在硬件和軟件間重新區(qū)分功能。例如,如果在集成階段發(fā)現(xiàn)軟件不能有效地響應一個實 時事件,可以將該功能下移到 FPGA 級別,這樣就將原由軟件實現(xiàn)的功能轉(zhuǎn)化為硬件功能。

適應多種機體— —靈活、可重新編程的解決方案適于為多種機體構(gòu)架或針對多用途基礎設計的飛航測試線上可更換件 (LRU)。由于 USAF和 NATO 的多種機體采用從 MIL-STD-1553B 標準分離出來的協(xié)議,所以多種機體的 LRU 需要靈活、可編程的設計。某些設計實施了通過特殊的子地址或模式代碼協(xié)議進行尋址擴展的數(shù)據(jù)集。很多固定翼和可旋轉(zhuǎn)翼飛機同時采用了較老的 MIL-STD-1553A 和 MIL-STD-1553B LRU,這就要求總線控制器和總線監(jiān)視器能夠處理不同的協(xié)議。

四、對MIL-STD-1553 系統(tǒng)設計采用基于核心的實施

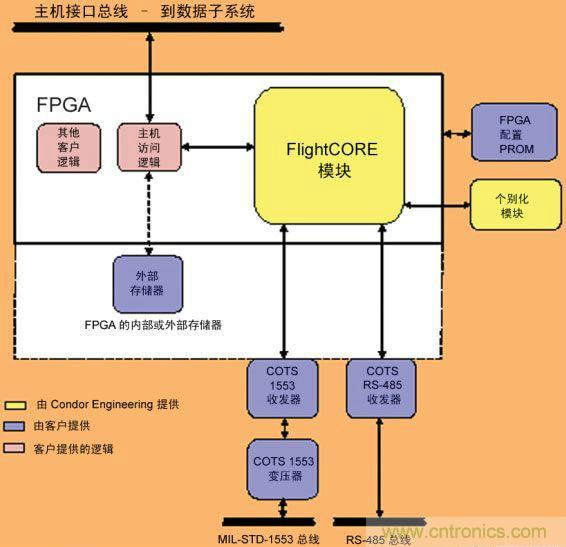

現(xiàn)代 FPGA 的強大功能使其成為 MIL-STD-1553 設計的理想選擇,這就是 Condor Engineering 推出 FlightCORE 的原因。FlightCORE 是一種允許設計人員在各種 Altera 和 Xilinx 的 FPGA中輕松實現(xiàn)無版權(quán)的實例化設計的 MIL-STD-1553 IP。多數(shù)情況下,利用Xilinx 綜合技術 (XST) 或 Altera Quartus II 集成綜合技術 (QIS),FlightCORE 1553 可以在兩天內(nèi)成功地集成。如圖 4 所示,用戶只須將 Condor Engineering 的 IP 核心與其自身邏輯和 Condor Engineering 的個別化模塊 (3mm x 3mm) 集成,即可實現(xiàn)高性能的 MIL-STD-1553設計。FlightCORE 還允許開發(fā)人員選擇存儲器的大小以恰好地與其系統(tǒng)需求相匹配。圖4還顯示了可以實施內(nèi)部存貯和/或外部雙端口隨機存貯器。該產(chǎn)品還提供了 Manchester II編碼與解碼、信息協(xié)議驗證與合法化及為接口控制和編程實施簡單的共享存貯架構(gòu)等所有的必要組件。只需增加外部收發(fā)器即可,如標準的COTS MIL-STD-1553或RS-485收發(fā)器。

單一芯片上集中多個實例,類似 Condor Engineering 的FlightCORE 這樣的 MIL-STD-1553 解決方案需要少量的FPGA資源,約為 3,000個邏輯單元,148k bit的內(nèi)存和不到 20個引腳(不包括外部主存總線)。較小的體積使在單一芯片上放置多個相互獨立的實例成為可能,如圖3 所示,某些程序可以在單一FPGA上集中8到10個實例。