【導(dǎo)讀】如前所述,是在PAL、GAL、EPLD、CPLD等可編程器件的基礎(chǔ)上進一步發(fā)展的產(chǎn)物。它是作為ASIC領(lǐng)域中的一種半定制電路而出現(xiàn)的,即解決了定制電路的不足,又克服了原有可編程器件門電路有限的缺點。

工作原理與簡介

如前所述,是在PAL、GAL、EPLD、CPLD等可編程器件的基礎(chǔ)上進一步發(fā)展的產(chǎn)物。它是作為ASIC領(lǐng)域中的一種半定制電路而出現(xiàn)的,即解決了定制電路的不足,又克服了原有可編程器件門電路有限的缺點。

由于需要被反復(fù)燒寫,它實現(xiàn)組合邏輯的基本結(jié)構(gòu)不可能像ASIC那樣通過固定的與非門來完成,而只能采用一種易于反復(fù)配置的結(jié)構(gòu)。查找表可以很好地滿足這一要求,目前主流FPGA都采用了基于SRAM工藝的查找表結(jié)構(gòu),也有一些軍品和宇航級FPGA采用Flash或者熔絲與反熔絲工藝的查找表結(jié)構(gòu)。通過燒寫文件改變查找表內(nèi)容的方法來實現(xiàn)對FPGA的重復(fù)配置。

根據(jù)數(shù)字電路的基本知識可以知道,對于一個n輸入的邏輯運算,不管是與或非運算還是異或運算等等,最多只可能存在2n種結(jié)果。所以如果事先將相應(yīng)的結(jié)果存放于一個存貯單元,就相當于實現(xiàn)了與非門電路的功能。FPGA的原理也是如此,它通過燒寫文件去配置查找表的內(nèi)容,從而在相同的電路情況下實現(xiàn)了不同的邏輯功能。

查找表(Look-Up-Table)簡稱為LUT,LUT本質(zhì)上就是一個RAM。目前FPGA中多使用4輸入的LUT,所以每一個LUT可以看成一個有4位地址線的 的RAM。 當用戶通過原理圖或HDL語言描述了一個邏輯電路以后,PLD/FPGA開發(fā)軟件會自動計算邏輯電路的所有可能結(jié)果,并把真值表(即結(jié)果)事先寫入RAM,這樣,每輸入一個信號進行邏輯運算就等于輸入一個地址進行查表,找出地址對應(yīng)的內(nèi)容,然后輸出即可。

下面給出一個4與門電路的例子來說明LUT實現(xiàn)邏輯功能的原理。

例1-1:給出一個使用LUT實現(xiàn)4輸入與門電路的真值表。

表1-1 4輸入與門的真值表

從中可以看到,LUT具有和邏輯電路相同的功能。實際上,LUT具有更快的執(zhí)行速度和更大的規(guī)模。

由于基于LUT的FPGA具有很高的集成度,其器件密度從數(shù)萬門到數(shù)千萬門不等,可以完成極其復(fù)雜的時序與邏輯組合邏輯電路功能,所以適用于高速、高密度的高端數(shù)字邏輯電路設(shè)計領(lǐng)域。其組成部分主要有可編程輸入/輸出單元、基本可編程邏輯單元、內(nèi)嵌SRAM、豐富的布線資源、底層嵌入功能單元、內(nèi)嵌專用單元等,主要設(shè)計和生產(chǎn)廠家有、Altera、Lattice、Actel、Atmel和QuickLogic等公司,其中最大的是、Altera、Lattice三家。

如前所述,F(xiàn)PGA是由存放在片內(nèi)的RAM來設(shè)置其工作狀態(tài)的,因此工作時需要對片內(nèi)RAM進行編程。用戶可根據(jù)不同的配置模式,采用不同的編程方式。FPGA有如下幾種配置模式:

并行模式:并行PROM、Flash配置FPGA;

主從模式:一片PROM配置多片F(xiàn)PGA;

串行模式:串行PROM配置FPGA;

外設(shè)模式:將FPGA作為微處理器的外設(shè),由微處理器對其編程。

目前,F(xiàn)PGA市場占有率最高的兩大公司和Altera生產(chǎn)的FPGA都是基于SRAM工藝的,需要在使用時外接一個片外存儲器以保存程序。上電時,F(xiàn)PGA將外部存儲器中的數(shù)據(jù)讀入片內(nèi)RAM,完成配置后,進入工作狀態(tài);掉電后FPGA恢復(fù)為白片,內(nèi)部邏輯消失。這樣FPGA不僅能反復(fù)使用,還無需專門的FPGA編程器,只需通用的EPROM、PROM編程器即可。Actel、QuickLogic等公司還提供反熔絲技術(shù)的FPGA,只能下載一次,具有抗輻射、耐高低溫、低功耗和速度快等優(yōu)點,在軍品和航空航天領(lǐng)域中應(yīng)用較多,但這種FPGA不能重復(fù)擦寫,開發(fā)初期比較麻煩,費用也比較昂貴。Lattice是ISP技術(shù)的發(fā)明者,在小規(guī)模PLD應(yīng)用上有一定的特色。早期的Xilinx產(chǎn)品一般不涉及軍品和宇航級市場,但目前已經(jīng)有Q Pro-R等多款產(chǎn)品進入該類領(lǐng)域。

1.2.2 FPGA芯片結(jié)構(gòu)

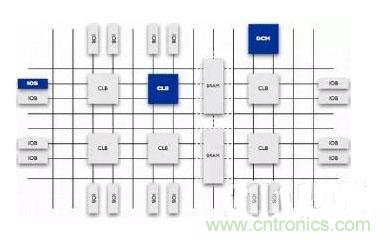

目前主流的FPGA仍是基于查找表技術(shù)的,已經(jīng)遠遠超出了先前版本的基本性能,并且整合了常用功能(如RAM、時鐘管理和DSP)的硬核(ASIC型)模塊。如圖1-1所示(注:圖1-1只是一個示意圖,實際上每一個系列的FPGA都有其相應(yīng)的內(nèi)部結(jié)構(gòu)),F(xiàn)PGA芯片主要由6部分完成,分別為:可編程輸入輸出單元、基本可編程邏輯單元、完整的時鐘管理、嵌入塊式RAM、豐富的布線資源、內(nèi)嵌的底層功能單元和內(nèi)嵌專用硬件模塊。

圖1-1 FPGA芯片的內(nèi)部結(jié)構(gòu)

每個模塊的功能如下:

1. 可編程輸入輸出單元(IOB)

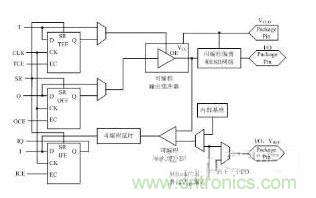

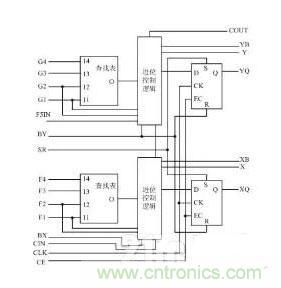

可編程輸入/輸出單元簡稱I/O單元,是芯片與外界電路的接口部分,完成不同電氣特性下對輸入/輸出信號的驅(qū)動與匹配要求,其示意結(jié)構(gòu)如圖1-2所示。FPGA內(nèi)的I/O按組分類,每組都能夠獨立地支持不同的I/O標準。通過軟件的靈活配置,可適配不同的電氣標準與I/O物理特性,可以調(diào)整驅(qū)動電流的大小,可以改變上、下拉電阻。目前,I/O口的頻率也越來越高,一些高端的FPGA通過DDR寄存器技術(shù)可以支持高達2Gbps的數(shù)據(jù)速率。

圖1-2 典型的IOB內(nèi)部結(jié)構(gòu)示意圖

外部輸入信號可以通過IOB模塊的存儲單元輸入到FPGA的內(nèi)部,也可以直接輸入FPGA 內(nèi)部。當外部輸入信號經(jīng)過IOB模塊的存儲單元輸入到FPGA內(nèi)部時,其保持時間(Hold Time)的要求可以降低,通常默認為0。

為了便于管理和適應(yīng)多種電器標準,F(xiàn)PGA的IOB被劃分為若干個組(bank),每個bank的接口標準由其接口電壓VCCO決定,一個bank只能有一種VCCO,但不同bank的VCCO可以不同。只有相同電氣標準的端口才能連接在一起,VCCO電壓相同是接口標準的基本條件。

2. 可配置邏輯塊(CLB)

CLB是FPGA內(nèi)的基本邏輯單元。CLB的實際數(shù)量和特性會依器件的不同而不同,但是每個CLB都包含一個可配置開關(guān)矩陣,此矩陣由4或6個輸入、一些選型電路(多路復(fù)用器等)和觸發(fā)器組成。 開關(guān)矩陣是高度靈活的,可以對其進行配置以便處理組合邏輯、移位寄存器或RAM。在Xilinx公司的FPGA器件中,CLB由多個(一般為4個或2個)相同的Slice和附加邏輯構(gòu)成,如圖1-3所示。每個CLB模塊不僅可以用于實現(xiàn)組合邏輯、時序邏輯,還可以配置為分布式RAM和分布式ROM。

圖1-3 典型的CLB結(jié)構(gòu)示意圖

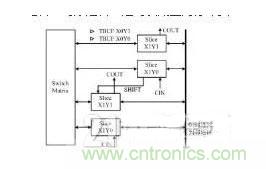

Slice是Xilinx公司定義的基本邏輯單位,其內(nèi)部結(jié)構(gòu)如圖1-4所示,一個Slice由兩個4輸入的函數(shù)、進位邏輯、算術(shù)邏輯、存儲邏輯和函數(shù)復(fù)用器組成。算術(shù)邏輯包括一個異或門(XORG)和一個專用與門(MULTAND),一個異或門可以使一個Slice實現(xiàn)2bit全加操作,專用與門用于提高乘法器的效率;進位邏輯由專用進位信號和函數(shù)復(fù)用器(MUXC)組成,用于實現(xiàn)快速的算術(shù)加減法操作;4輸入函數(shù)發(fā)生器用于實現(xiàn)4輸入LUT、分布式RAM或16比特移位寄存器(Virtex-5系列芯片的Slice中的兩個輸入函數(shù)為6輸入,可以實現(xiàn)6輸入LUT或64比特移位寄存器);進位邏輯包括兩條快速進位鏈,用于提高CLB模塊的處理速度。

圖1-4 典型的4輸入Slice結(jié)構(gòu)示意圖

3. 數(shù)字時鐘管理模塊(DCM)

業(yè)內(nèi)大多數(shù)FPGA均提供數(shù)字時鐘管理(Xilinx的全部FPGA均具有這種特性)。Xilinx推出最先進的FPGA提供數(shù)字時鐘管理和相位環(huán)路鎖定。相位環(huán)路鎖定能夠提供精確的時鐘綜合,且能夠降低抖動,并實現(xiàn)過濾功能。

4. 嵌入式塊RAM(BRAM)

大多數(shù)FPGA都具有內(nèi)嵌的塊RAM,這大大拓展了FPGA的應(yīng)用范圍和靈活性。塊RAM可被配置為單端口RAM、雙端口RAM、內(nèi)容地址存儲器(CAM)以及FIFO等常用存儲結(jié)構(gòu)。RAM、FIFO是比較普及的概念,在此就不冗述。CAM存儲器在其內(nèi)部的每個存儲單元中都有一個比較邏輯,寫入CAM中的數(shù)據(jù)會和內(nèi)部的每一個數(shù)據(jù)進行比較,并返回與端口數(shù)據(jù)相同的所有數(shù)據(jù)的地址,因而在路由的地址交換器中有廣泛的應(yīng)用。除了塊RAM,還可以將FPGA中的LUT靈活地配置成RAM、ROM和FIFO等結(jié)構(gòu)。在實際應(yīng)用中,芯片內(nèi)部塊RAM的數(shù)量也是選擇芯片的一個重要因素。

單片塊RAM的容量為18k比特,即位寬為18比特、深度為1024,可以根據(jù)需要改變其位寬和深度,但要滿足兩個原則:首先,修改后的容量(位寬 深度)不能大于18k比特;其次,位寬最大不能超過36比特。當然,可以將多片塊RAM級聯(lián)起來形成更大的RAM,此時只受限于芯片內(nèi)塊RAM的數(shù)量,而不再受上面兩條原則約束。

5. 豐富的布線資源

布線資源連通FPGA內(nèi)部的所有單元,而連線的長度和工藝決定著信號在連線上的驅(qū)動能力和傳輸速度。FPGA芯片內(nèi)部有著豐富的布線資源,根據(jù)工藝、長度、寬度和分布位置的不同而劃分為4類不同的類別。第一類是全局布線資源,用于芯片內(nèi)部全局時鐘和全局復(fù)位/置位的布線;第二類是長線資源,用以完成芯片Bank間的高速信號和第二全局時鐘信號的布線;第三類是短線資源,用于完成基本邏輯單元之間的邏輯互連和布線;第四類是分布式的布線資源,用于專有時鐘、復(fù)位等控制信號線。

在實際中設(shè)計者不需要直接選擇布線資源,布局布線器可自動地根據(jù)輸入邏輯網(wǎng)表的拓撲結(jié)構(gòu)和約束條件選擇布線資源來連通各個模塊單元。從本質(zhì)上講,布線資源的使用方法和設(shè)計的結(jié)果有密切、直接的關(guān)系。

6. 底層內(nèi)嵌功能單元

內(nèi)嵌功能模塊主要指DLL(Delay Locked Loop)、PLL(Phase Locked Loop)、DSP和CPU等軟處理核(Soft Core)?,F(xiàn)在越來越豐富的內(nèi)嵌功能單元,使得單片F(xiàn)PGA成為了系統(tǒng)級的設(shè)計工具,使其具備了軟硬件聯(lián)合設(shè)計的能力,逐步向SOC平臺過渡。

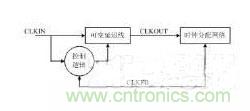

DLL和PLL具有類似的功能,可以完成時鐘高精度、低抖動的倍頻和分頻,以及占空比調(diào)整和移相等功能。Xilinx公司生產(chǎn)的芯片上集成了DLL,Altera公司的芯片集成了PLL,Lattice公司的新型芯片上同時集成了PLL和DLL。PLL 和DLL可以通過IP核生成的工具方便地進行管理和配置。DLL的結(jié)構(gòu)如圖1-5所示。

圖1-5 典型的DLL模塊示意圖

7. 內(nèi)嵌專用硬核

內(nèi)嵌專用硬核是相對底層嵌入的軟核而言的,指FPGA處理能力強大的硬核(Hard Core),等效于ASIC電路。為了提高FPGA性能,芯片生產(chǎn)商在芯片內(nèi)部集成了一些專用的硬核。例如:為了提高FPGA的乘法速度,主流的FPGA中都集成了專用乘法器;為了適用通信總線與接口標準,很多高端的FPGA內(nèi)部都集成了串并收發(fā)器(SERDES),可以達到數(shù)十Gbps的收發(fā)速度。

Xilinx公司的高端產(chǎn)品不僅集成了Power PC系列CPU,還內(nèi)嵌了DSP Core模塊,其相應(yīng)的系統(tǒng)級設(shè)計工具是EDK和Platform Studio,并依此提出了片上系統(tǒng)(System on Chip)的概念。通過PowerPC、Miroblaze、Picoblaze等平臺,能夠開發(fā)標準的DSP處理器及其相關(guān)應(yīng)用,達到SOC的開發(fā)目的。

1.2.3 軟核、硬核以及固核的概念

IP(Intelligent Property)核是具有知識產(chǎn)權(quán)核的集成電路芯核總稱,是經(jīng)過反復(fù)驗證過的、具有特定功能的宏模塊,與芯片制造工藝無關(guān),可以移植到不同的半導(dǎo)體工藝中。到了SOC階段,IP核設(shè)計已成為ASIC電路設(shè)計公司和FPGA提供商的重要任務(wù),也是其實力體現(xiàn)。對于FPGA開發(fā)軟件,其提供的IP核越豐富,用戶的設(shè)計就越方便,其市場占用率就越高。目前,IP核已經(jīng)變成系統(tǒng)設(shè)計的基本單元,并作為獨立設(shè)計成果被交換、轉(zhuǎn)讓和銷售。

從IP核的提供方式上,通常將其分為軟核、硬核和固核這3類。從完成IP核所花費的成本來講,硬核代價最大;從使用靈活性來講,軟核的可復(fù)用使用性最高。

1. 軟核

軟核在EDA設(shè)計領(lǐng)域指的是綜合之前的寄存器傳輸級(RTL)模型;具體在FPGA設(shè)計中指的是對電路的硬件語言描述,包括邏輯描述、網(wǎng)表和幫助文檔等。軟核只經(jīng)過功能仿真,需要經(jīng)過綜合以及布局布線才能使用。其優(yōu)點是靈活性高、可移植性強,允許用戶自配置;缺點是對模塊的預(yù)測性較低,在后續(xù)設(shè)計中存在發(fā)生錯誤的可能性,有一定的設(shè)計風險。軟核是IP核應(yīng)用最廣泛的形式。

2. 固核

固核在EDA設(shè)計領(lǐng)域指的是帶有平面規(guī)劃信息的網(wǎng)表;具體在FPGA設(shè)計中可以看做帶有布局規(guī)劃的軟核,通常以RTL代碼和對應(yīng)具體工藝網(wǎng)表的混合形式提供。將RTL描述結(jié)合具體標準單元庫進行綜合優(yōu)化設(shè)計,形成門級網(wǎng)表,再通過布局布線工具即可使用。和軟核相比,固核的設(shè)計靈活性稍差,但在可靠性上有較大提高。目前,固核也是IP核的主流形式之一。

3. 硬核

硬核在EDA設(shè)計領(lǐng)域指經(jīng)過驗證的設(shè)計版圖;具體在FPGA設(shè)計中指布局和工藝固定、經(jīng)過前端和后端驗證的設(shè)計,設(shè)計人員不能對其修改。不能修改的原因有兩個:首先是系統(tǒng)設(shè)計對各個模塊的時序要求很嚴格,不允許打亂已有的物理版圖;其次是保護知識產(chǎn)權(quán)的要求,不允許設(shè)計人員對其有任何改動。IP硬核的不許修改特點使其復(fù)用有一定的困難,因此只能用于某些特定應(yīng)用,使用范圍較窄。