【導(dǎo)讀】犯錯乃人之常情�����。但對于系統(tǒng)的模數(shù)轉(zhuǎn)換器(ADC),我們能夠提出什么樣的要求呢���?我們將回顧轉(zhuǎn)換誤差率(CER)測試的范圍和高速ADC的分析�。取決于采樣速率和所需的目標(biāo)限值�����,ADC CER測量過程可能需要數(shù)周或數(shù)月時間����。為實現(xiàn)高置信度(CL),出現(xiàn)首次錯誤之后常常還需要進行測試(Redd�����,2000)����。對于那些要求低轉(zhuǎn)換誤差率的系統(tǒng),需要付出努力來詳盡地予以量化����。一切完成后����,我們便能確定高置信度的誤差率—優(yōu)于10–15�。

許多實際高速采樣系統(tǒng),如電氣測試與測量設(shè)備�����、生命系統(tǒng)健康監(jiān)護��、雷達和電子戰(zhàn)對抗等����,不能接受較高的ADC轉(zhuǎn)換誤差率。這些系統(tǒng)要在很寬的噪聲頻譜上尋找極其罕見或極小的信號����。誤報警可能會引起系統(tǒng)故障。因此��,我們必須能夠量化高速ADC轉(zhuǎn)換誤差率的頻率和幅度���。

CER與BER

首先�����,讓我們理清誤差率描述中的兩大差異���。轉(zhuǎn)換誤差率(CER)通常是ADC關(guān)于模擬電壓采樣的判斷不正確的結(jié)果,因此����,與轉(zhuǎn)換器輸入的滿量程范圍相比較,其相應(yīng)的數(shù)字碼也不正確�����。ADC的誤碼率(BER)也能描述類似的誤差���,但就我們的討論而言����,我們把BER定義為純數(shù)字接收錯誤�;如果沒有這種錯誤,那么轉(zhuǎn)換的碼數(shù)據(jù)就是正確的��。這種情況下�����,正確的ADC數(shù)字輸出未能被FPGA或ASIC等下游邏輯器件正確接收到。代碼出錯的程度及其出現(xiàn)的頻率就是本文余下部分要討論的內(nèi)容����。

僅僅閱讀數(shù)據(jù)手冊中的技術(shù)參數(shù),可能難以掌握ADC轉(zhuǎn)換誤差���。使用轉(zhuǎn)換器數(shù)據(jù)手冊中的單個數(shù)據(jù)����,當(dāng)然可以對轉(zhuǎn)換誤差率進行某種估計����,但該數(shù)據(jù)量化的到底是什么呢?您無從判斷多大的樣本偏差可被視為錯誤���,無法確定試驗測量或仿真的置信度��。必須將“錯誤”定義限定在已知出現(xiàn)頻率所對應(yīng)的幅度以內(nèi)�。

誤差源

有多種誤差源會造成ADC轉(zhuǎn)換錯誤���,內(nèi)部和外部均有�。外部誤差源包括系統(tǒng)電源毛刺、接地反彈���、異常大的時鐘抖動和可能有錯的控制命令��。ADC數(shù)據(jù)手冊中的建議和應(yīng)用筆記通常會說明避開這些外部問題的最佳系統(tǒng)布局做法。ADC內(nèi)部誤差源主要可歸因于亞穩(wěn)態(tài)(Beavers����,2014)或模擬域中各級之間的殘余處理傳遞,以及數(shù)字域和物理層中的輸出時序誤差��。ADC設(shè)計團隊在器件開發(fā)過程中必須分析這些挑戰(zhàn)���。

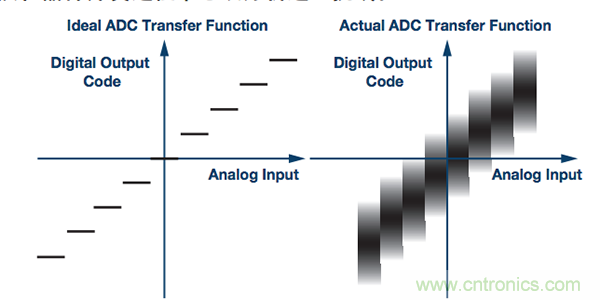

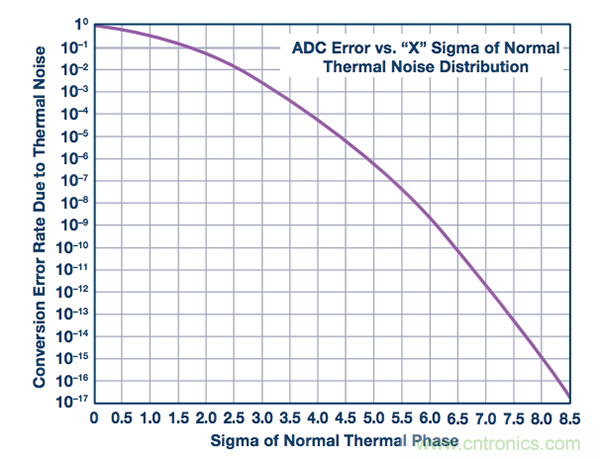

圖1. 對于滿量程上模擬分辨率的各個位����,理想ADC樣本都有單一數(shù)字輸出(左圖)����。實際ADC輸出行為的一個例子(右圖)顯示了與內(nèi)部和外部噪聲相關(guān)的某種模糊性。

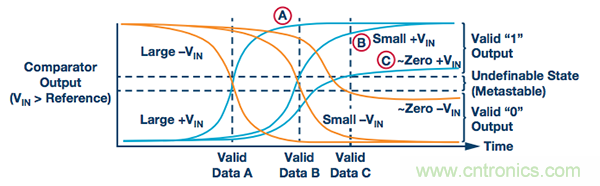

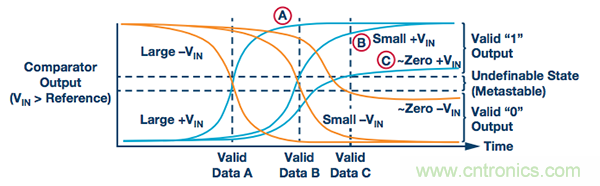

在一組比較器中����,當(dāng)比較器基準(zhǔn)電壓精確等于或極其接近待比較的電壓時���,便可能發(fā)生亞穩(wěn)態(tài)狀況(Kester,2006)�����。比較電壓在幅度上越接近基準(zhǔn)電壓����,比較器作出全面判斷所需的時間就越長。如果二者之間的電壓差非常小或為0�����,比較器可能沒有足夠的時間來最終判定比較電壓是高于還是低于基準(zhǔn)電壓����。當(dāng)該樣本的轉(zhuǎn)換完成時,比較器輸出可能處于亞穩(wěn)第三態(tài)�,而不是清晰地判定一個有效邏輯輸出1或0 (Kester,2006)����。這種猶豫不定會波及整個ADC,可能引起轉(zhuǎn)換錯誤����。

圖2. 對于滿量程上模擬分辨率的各個位����,理想ADC樣本都有單一數(shù)字輸出(左圖)�。實際ADC輸出行為的一個例子(右圖)顯示了與內(nèi)部和外部噪聲相關(guān)的某種模糊性

在流水線型ADC架構(gòu)中,還有其他潛在轉(zhuǎn)換誤差源�,即在級間邊界傳遞處,殘余電壓從上一級傳送到下一級�����。例如��,若兩級之間有未校正的增益匹配誤差�����,則殘余電壓的傳遞會在后續(xù)級中產(chǎn)生誤差��。此外����,負責(zé)將一個電壓發(fā)送到下一ADC級的殘余DAC中的毛刺也可能在稍后的處理中引起意外的干擾誤差(Kester�����,2006)。任何無源元件中都存在的熱噪聲是所有ADC固有的噪聲分量����,它決定了ADC處理的絕對噪底(Brannon,2003)��。在詳細測定ADC的過程中��,必須審視和量化所有這些可能的誤差源����,確保轉(zhuǎn)換器運行時沒有任何落差。

噪聲分量

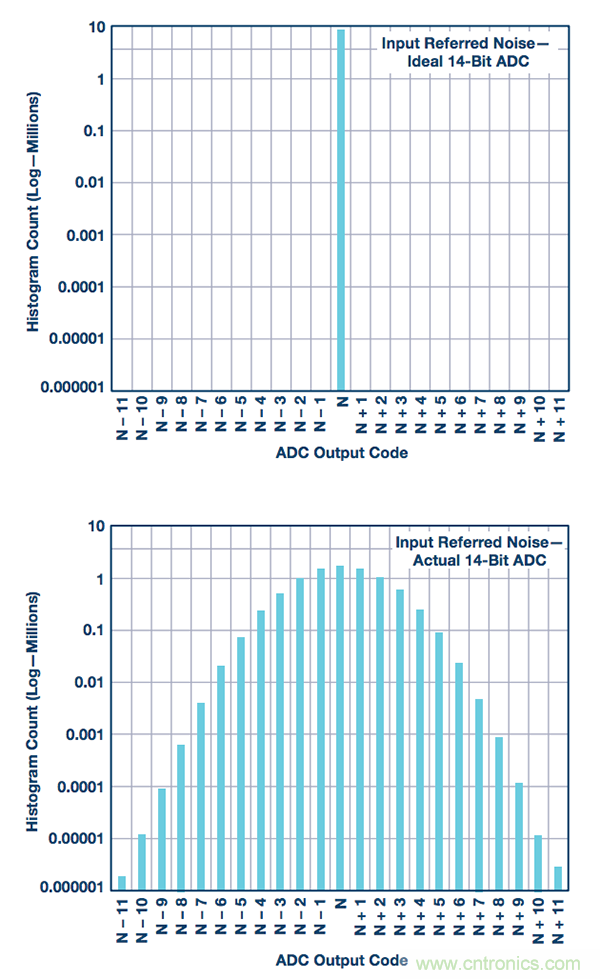

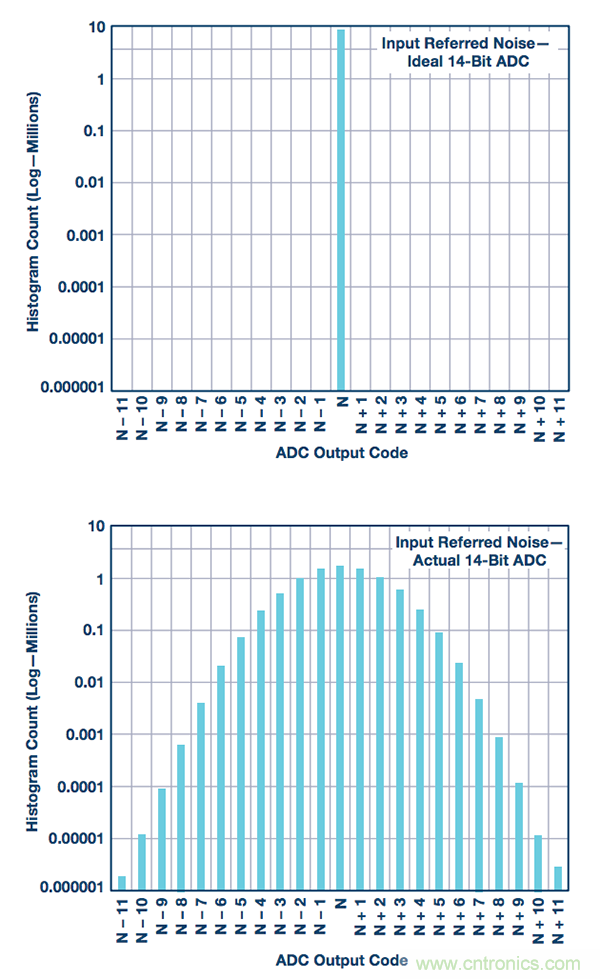

折合到輸入端的噪聲是ADC轉(zhuǎn)換缺陷的一個固有分量�����,其中包括ADC輸入端的熱噪聲���。常常利用ADC輸入端開路或浮空情況下的數(shù)字輸出碼直方圖來對其進行量化�。ADC數(shù)據(jù)手冊通常會說明并顯示此噪聲�����。下面的圖形給出了此噪聲幅度的例子,其在本例中為[N] ± 11��。

圖3. 輸入端開路或浮空時���,理想ADC會采樣輸出一個中間電平失調(diào)碼��,如左側(cè)直方圖所示�����。實際ADC會有折合到輸入端的噪聲����,其在對數(shù)尺度上應(yīng)表現(xiàn)為高斯形狀的彎曲直方圖(右側(cè))����。

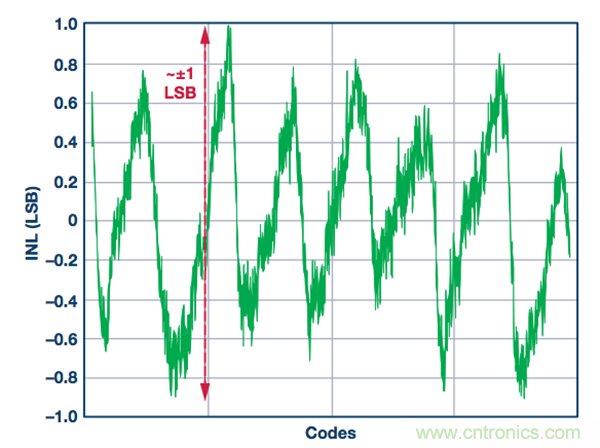

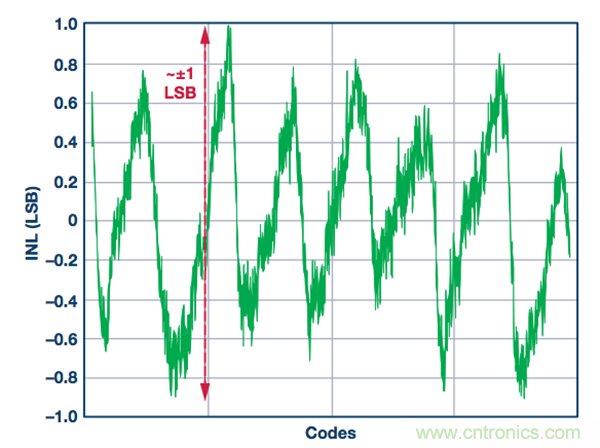

ADC的積分非線性(INL)是ADC滿量程輸入范圍內(nèi)實際樣本編碼相對于理想輸出的傳遞函數(shù)(Kester�����,2005)����。ADC數(shù)據(jù)手冊通常也會說明此信息并給出其曲線����。與理想編碼的最大偏差通常用某一數(shù)量的LSB來表示�����。下面是INL曲線示例����。雖然它反映了一定量的絕對誤差,但在大部分16位或稍低分辨率的高速ADC中���,INL通常只有0到3個碼����。它不是轉(zhuǎn)換器實際誤差率的主要貢獻因素��。

圖4. INL曲線示例�,在所有ADC編碼上測量,與理想樣本相比�����,最大誤差為±1 LSB或±1個碼,對ADC轉(zhuǎn)換誤差而言基本上可忽略不計����。

測試方法

針對長期CER檢測,測試方法可以使用非常低的ADC輸入頻率(相對于時鐘速率而言)�����。在任何兩個相鄰樣本點之間構(gòu)成一條直線���,正弦波斜率可近似為該直線的斜率��。類似地����,略高于采樣速率的輸入頻率會混疊為低頻���。對于這種情況�����,有一個可預(yù)測的理想解決方案能讓各相鄰樣本處于前一樣本的±1個碼內(nèi)。輸入信號頻率和編碼采樣時鐘頻率必須鎖定�����,保持可預(yù)測的相位對齊。如果此相位不是恒定值�,對齊就會異相,測量數(shù)據(jù)將沒有用處����。因此,為了計算理想轉(zhuǎn)換結(jié)果�,樣本(N + 1) – sample

(N)應(yīng)相差一個碼,幅度不超過1�����。

所有ADC固有的可預(yù)測小轉(zhuǎn)換誤差源包括積分非線性����、輸入噪聲、時鐘抖動和量化噪聲�����。所有這些噪聲貢獻都可以累加以獲得最差限值�����,若超過此限值,誤差將被視為來自兩個相鄰轉(zhuǎn)換樣本�����。16位ADC的輸出編碼數(shù)是12位轉(zhuǎn)換器的24或16倍�����。因此����,該擴展分辨率會影響用于限制轉(zhuǎn)換誤差率測試的編碼數(shù)。在其他一切都相同時����,16位ADC的限值將被12位ADC寬16倍?�?墒褂肁DC內(nèi)置自測(BIST)功能并根據(jù)熱噪聲����、時鐘抖動和其他系統(tǒng)非線性來確定誤差閾值。當(dāng)超過誤差限值時�,可在ADC內(nèi)核中標(biāo)記特定樣本及其對應(yīng)的樣本數(shù)和誤差幅度��。使用內(nèi)部BIST的一大好處,是它將誤差源界定在ADC內(nèi)核本身�����,排除了專屬于數(shù)字數(shù)據(jù)傳輸輸出的接收位錯誤引起的誤差�����。一旦明確誤差閾值���,便可執(zhí)行涉及ADC�����、鏈路以及FPGA或ASIC的完整系統(tǒng)測量����,以便確定全分量CER����。

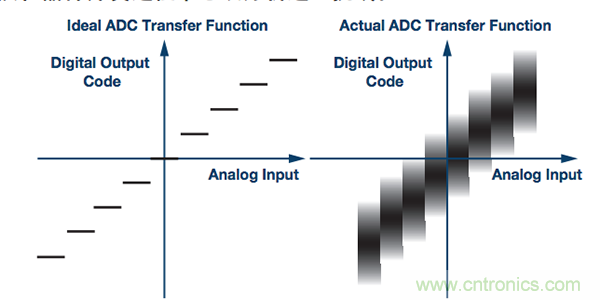

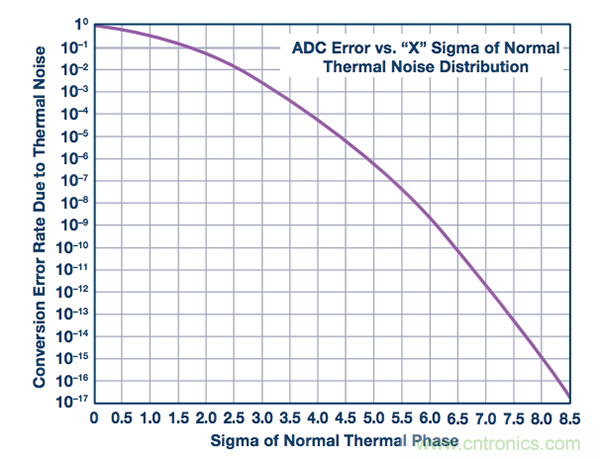

圖5. ADC轉(zhuǎn)換誤差率與其熱噪聲的關(guān)系通常只能通過晶體管級電路仿真獲得。上圖為一個12位ADC的示例圖�����,要實現(xiàn)10–15的CER,其必須能承受8 Σ的熱噪聲����。

現(xiàn)在看看如何計算熱噪聲貢獻(Brannon,2003)�����。

SNR = 20log(VSIGNAL/VNOISE)

VNOISE = VSIGNAL × 10^(–SNR/20)

為得出ADC的均方根噪聲�����,必須調(diào)整VFULLSCALE:

VNOISE = (VFULLSCALE/(2 × (2) × 10^(–SNR/20)

利用以下公式計算AD9625的熱噪聲限值����,它是一款12位2.6 GSPS ADC,設(shè)計滿量程范圍(FSR)為1.1 V�����,SNR為55��,2.508 MHz混疊輸入頻率�。熱噪聲限值 = 8 × VINpp × 10 ^ (SNR/20)/2√(2) = 3.39 mV ~±12個碼。

本例中��,對于10–15誤差限值,單單熱噪聲的8Σ分布就能貢獻最多±12個碼����。這應(yīng)針對ADC的折合到輸入端總噪聲測量進行測試����。注意:數(shù)據(jù)手冊中的折合到輸入端噪聲可能不是基于足夠大的樣本規(guī)模(用于10–15測試)而測得的。折合到輸入端噪聲包含所有內(nèi)部噪聲源�����,包括熱噪聲��。

為了明確界限以盡可能包含所有噪聲源���,包括測試設(shè)備�,我們使用內(nèi)部BIST來測量誤差幅度分布���。利用AD9625的內(nèi)部BIST�����,以2.5 GSPS運行�����,混疊AIN頻率為80 kHz�,接近ADC滿量程,使用標(biāo)稱

電源和溫度條件執(zhí)行CER測量���,為期20天�����。

假設(shè)模擬電壓轉(zhuǎn)換為數(shù)字表示的所有ADC處理都是理想的�����。數(shù)字數(shù)據(jù)仍然需要精確傳輸�����,并在信號鏈的下游FPGA或ASIC中的下一級處理中精確接收�����。這一級的數(shù)字混亂通常由位錯誤或誤碼率來定義�����。然而����,ADC的數(shù)據(jù)眼圖輸出的綜合特性可以在PCB走線末端直接測量,并與JESD204B接收器眼罩比較����,從而非常好地了解輸出質(zhì)量(Farrelly�,Loberg 2013)1。

在1 Σ內(nèi)以2.6 GSPS運行時�,為了確立10–15的CER,10的15次方個樣本�����,需要讓此測試連續(xù)運行4.6天��。對于更大的Σ�����,要確立更高的置信度����,此測試需要運行更長時間2����。測試需要非常穩(wěn)定的

測試環(huán)境和干凈的電源����。被測轉(zhuǎn)換器的電壓源如有任何毛刺未被抑制,將導(dǎo)致測量錯誤����,測試將不得不從頭再來。

可利用一個FPGA計數(shù)器來記錄兩個相鄰樣本的幅度差超過閾值的情況�����,把該樣本算作一次轉(zhuǎn)換錯誤�。計數(shù)器必須累計整個測試期間的錯誤總數(shù)。為了確保系統(tǒng)的工作行為符合預(yù)期�����,誤差幅度和理想值也應(yīng)記錄在直方圖中���。測試所需時間取決于采樣速率����、期望的測試轉(zhuǎn)換誤差率和置信度要求。小于10–15的CER和95%的置信度至少需要連續(xù)測試14天��。通過外推到實測值以外可以估計CER�����,但置信度會降低(Redd�����,2000)��。

測量ADC的CER是一個破費時間的過程�����,您可能會想�����,是否能夠基于已知測量結(jié)果進行外推�����。好消息是可以這樣做�。然而,有利必有弊�����,讀者要擦亮眼睛�。當(dāng)我們不斷地利用這種方法對誤差率進行合理的數(shù)學(xué)估計時,估計的置信度會越來越低3��。例如�,若置信度不到1%,那么知道10–18的誤差率可能也沒有什么用�����。

對于任何給定樣本�����,轉(zhuǎn)換誤差閾值可能累計達到4或5個LSB�����。根據(jù)ADC分辨率�����、系統(tǒng)性能和應(yīng)用的誤差率要求,該值的大小可能略有不同���。使用此誤差帶與理想值進行比較后�����,超出此限值的樣本將被視為轉(zhuǎn)換錯誤����。ADC的誤差帶可通過調(diào)整閾值并監(jiān)視典型性能數(shù)據(jù)來測試��。最后使用的測試限值為缺陷的均方根和����,其中主要是ADC熱噪聲���。

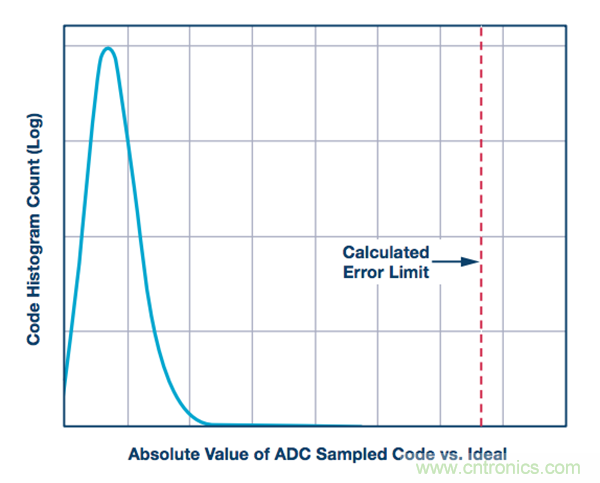

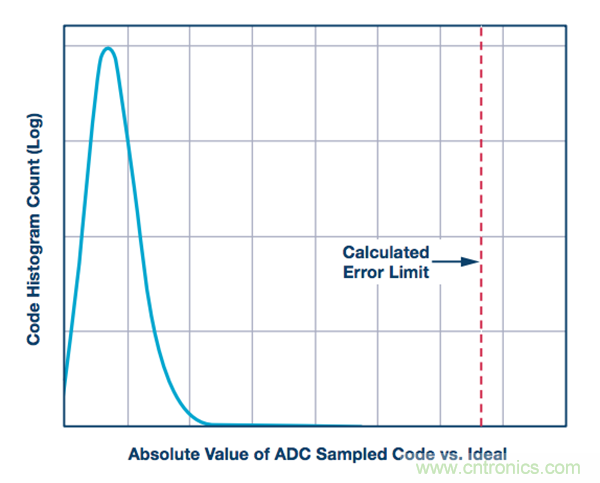

采樣值相對于理想值的測試數(shù)據(jù)直方圖類似于離散式泊松分布圖����。泊松分布與二項式分布的主要區(qū)別在于�����,泊松分布沒有固定的試驗次數(shù)。相反����,它使用固定的時間或空間間隔,并記錄其中的成功次數(shù)�,這與上述CER測試方法相似。記錄到的任何樣本如超出根據(jù)理想值算得的誤差限值�����,就會被視為真正的碼錯誤�����。

圖6. 利用ADC樣本與理想輸出碼相比較的長期直方圖���,我們可以檢測任何超出計算限值的偏差����。該直方圖類似于泊松分布圖����。

系統(tǒng)

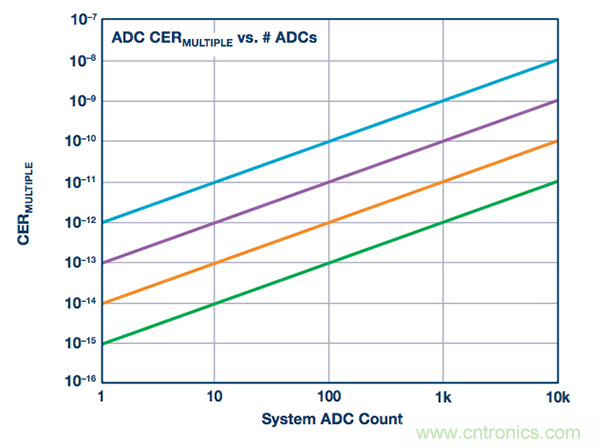

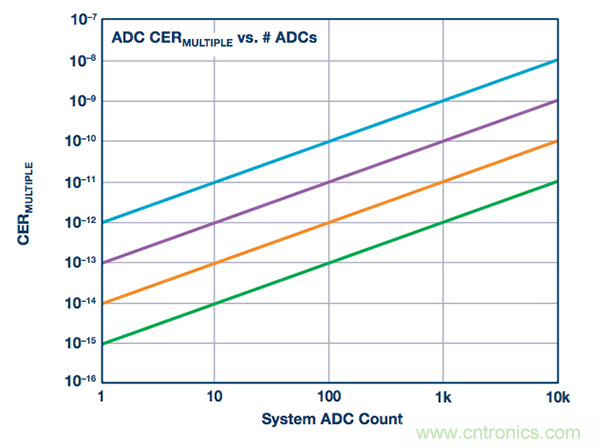

懂得單個轉(zhuǎn)換器的CER之后���,我們便可計算一個包含許多轉(zhuǎn)換器的高級同步系統(tǒng)的誤差率。許多系統(tǒng)工程師會問:在一個使用大量ADC的大型復(fù)雜系統(tǒng)中����,累積ADC轉(zhuǎn)換誤差率將是多少?

因此���,對于高級多信號采集系統(tǒng)���,第二考慮事項就是確定一系列(而不是某一個)轉(zhuǎn)換器的轉(zhuǎn)換誤差率。乍看之下����,這似乎是一個令人怯步的任務(wù)。幸運的是���,測得或算得單個ADC的CER之

后�����,將此誤差率外推到多個ADC并不是那么困難。這樣����,函數(shù)就變成基于系統(tǒng)所用轉(zhuǎn)換器數(shù)目的概率擴張方程��。

首先�,求出單個轉(zhuǎn)換器不發(fā)生錯誤的概率���。它僅比1略小一點�����,即1減去誤差率值(1–CERSINGLE)�����。其次�����,系統(tǒng)中有多少個ADC��,便將該概率自乘多少次����,即(1–CERSINGLE)#ADCs���。最后��,將1減去上述值�����,便可得出系統(tǒng)會出錯的誤差率����。我們得到以下方程:

CERMULTIPLE = 1 – (1 – CERSINGLE)#ADCs

考慮一個使用99個ADC,單個ADC的CER為10–15的系統(tǒng)����。

1 – CERSINGLE = 0.999999999999999

CERMULTIPLE = 1 – (0.999999999999999)

99 =9.8999999999995149000000000799095 × 10–14 (~about 10–13)

可以看出,現(xiàn)在的CERMULTIPLE值幾乎比CERSINGLE (10–15)大100倍��。由此可以得知����,含有99個ADC的系統(tǒng)的轉(zhuǎn)換誤差率大致等于單個ADC的CER乘以系統(tǒng)中的ADC數(shù)量。從根本上說�����,它高于單個ADC的轉(zhuǎn)換誤差率�,既受單個ADC轉(zhuǎn)換誤差率的限制,也受系統(tǒng)所用轉(zhuǎn)換器數(shù)量的限制�����。因此���,我們可以得出結(jié)論:包含許多ADC的系統(tǒng)與單個ADC相比����,總轉(zhuǎn)換誤差率會顯著提高��。

圖7. 使用多個轉(zhuǎn)換器的系統(tǒng)的CER正比于單個轉(zhuǎn)換器的CER乘以ADC數(shù)量�����。

確定ADC轉(zhuǎn)換誤差可能很困難�����,但仍是可實現(xiàn)的�����。第一步是確定系統(tǒng)中的轉(zhuǎn)換誤差大致有多大����。然后需要確定一組適當(dāng)?shù)挠薪缯`差限值�����,包括預(yù)期ADC操作的非線性良性源��。最后����,特定測量算法可實現(xiàn)大部分或全部測試�。測量結(jié)果可外推到測試界限之外,以獲得額外的近似�����。

參考文獻

Beavers���,Ian����。“高速ADC的轉(zhuǎn)換誤差率解密����。”EDN���,2014年���。

Brannon����,Brad�。“ADC噪聲對無線系統(tǒng)性能影響的分析。”EE Times���,2003年�����。

Frank Farrelly和Chris Loberg����。“更快的JESD204B標(biāo)準(zhǔn)帶來驗證挑戰(zhàn)����。”Electronic Design,2013年。

Kester�����,Walt�����。“MT-011:找出那些難以琢磨���、稍縱即逝的閃碼和亞穩(wěn)狀態(tài)�。”指南MT-011�����,ADI公司�����,2006年����。

Kester,Walt���。“MT-004:ADC輸入噪聲面面觀—噪聲是利還是弊���?���。”指南MT-004,ADI公司�,2005年10月。

Redd�����,Justin�����。“計算誤差概率估計的統(tǒng)計置信度�����。”Lightwave�,2000年����。

Redd�����,Justin�����。“誤碼率測試解密��。”Lightwave Online�,2004年����。Jeffrey Ugalde和Ian Beavers。“設(shè)計低誤碼率的JESD204B轉(zhuǎn)換器系統(tǒng)����。”EDN,2014年���。

Wolaver���,Dan H。“快速精確地測量誤差率���。”Electronic Design����,1995年。

尾注

1 雖然本文未做詳細討論����,但ADC接收器的數(shù)字數(shù)據(jù)眼的質(zhì)量以及相應(yīng)的數(shù)字鏈路BER可歸因于許多因素,包括預(yù)加重����、PCB材料、碼間干擾和走線長度���。

2 欲更詳細了解CER測試的置信度,請參閱(Redd�����,2000)和(Beavers����,2014)

本文轉(zhuǎn)載自ADI電機控制中文技術(shù)社區(qū)。

推薦閱讀: