【導讀】DDR布線在PCB設計中占有舉足輕重的地位,設計成功的關鍵就是要保證系統(tǒng)有充足的時序裕量。要保證系統(tǒng)的時序,線長匹配又是一個重要的環(huán)節(jié)。

我們來回顧一下,DDR布線,線長匹配的基本原則是:地址,控制/命令信號與時鐘做等長。數(shù)據(jù)信號與DQS做等長。為啥要做等長?大家會說是要讓同組信號同時到達接收端,好讓接收芯片能夠同時處理這些信號。那么,時鐘信號和地址同時到達接收端,波形的對應關系是什么樣的呢?我們通過仿真來看一下具體波形。

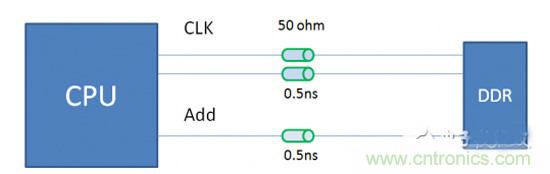

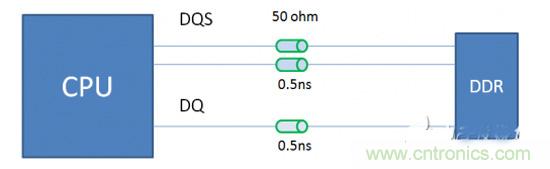

建立如下通道,分別模擬DDR3的地址信號與時鐘信號。

圖1.地址/時鐘仿真示意圖

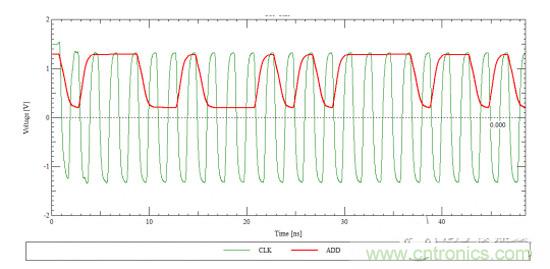

為方便計算,我們假設DDR的時鐘頻率為500MHz,這樣對應的地址信號的速率就應該是500Mbps,這里大家應該明白,雖然DDR是雙倍速率,但對于地址/控制信號來說,依然是單倍速率的。下面來看看波形,在地址與時鐘完全等長的情況下,地址與數(shù)據(jù)端的接收波形如下圖2,紅色代表地址信號,綠色代表時鐘信號。

圖2.時鐘信號與地址信號波形

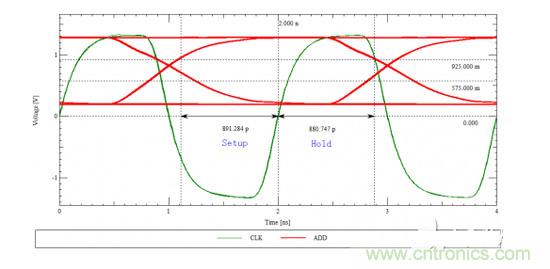

上面的波形我們似乎看不出時鐘與地址之間的時序關系是什么樣的,我們把它放在一個眼圖中,時序關系就很明確了。這里粗略的計算下建立時間與保持時間。如下圖

圖3.時鐘信號與地址信號波形

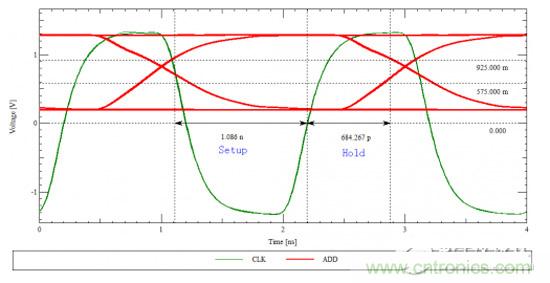

由上圖3.我們可以知道,該地址信號的建立時間大約為891ps,保持時間為881ps。這是在時鐘與地址信號完全等長情況下的波形。如果地址與時鐘不等長,信號又是什么樣的呢?仿真中,我們讓地址線比時鐘線慢200ps,得到的與眼圖如下:

圖4.時鐘信號與地址信號波形

由上圖可知,在地址信號比時鐘信號長的情況下,保持時間為684ps,建立越為1.1ns??梢?,相對于地址線與時鐘線等長來說,地址線比時鐘線長會使地址信號的建立時間更短。同理,如果時鐘線比地址線長,則建立時間會變長,而保持時間會變短。那么雙倍速率的數(shù)據(jù)信號又是怎樣的?下面通過具體的仿真實例來看一下。

圖5.DQ 與 DQS仿真示意

仿真通道如上圖所示,驅(qū)動端和接收端為某芯片公司的IBIS模型,仿真波形如下:

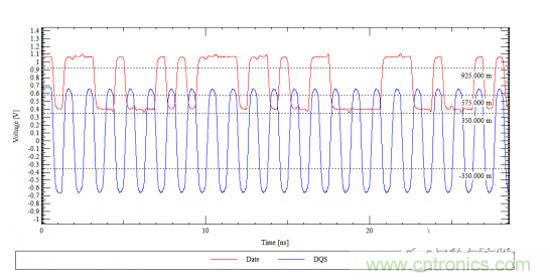

圖6.DQ與DQS仿真波形

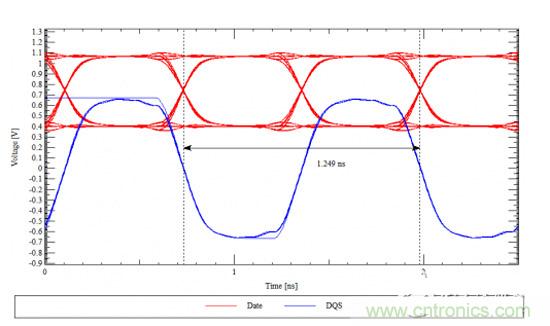

我們將DQS和DQ信號同時生成眼圖,在一個窗口下觀測,結果如下:

圖7.DQ與DQS眼圖

如上圖所示,大家可能發(fā)現(xiàn)了,如果按照原始對應關系,數(shù)據(jù)信號的邊沿和時鐘信號的邊沿是對齊的,如果是這樣,時鐘信號怎樣完成對數(shù)據(jù)信號的采樣呢?實際上并不是這樣的。以上仿真只是簡單的將兩波形放在了一起,因為DQ和DQS的傳輸通道長度是一樣的,所以他們的邊沿是對齊的。實際工作的時候,主控芯片會有一個調(diào)節(jié)機制。一般數(shù)據(jù)信號會比DQS提前四分之一周期被釋放出來,實際上,在顆粒端接收到的波形對應關系應該是這樣的:

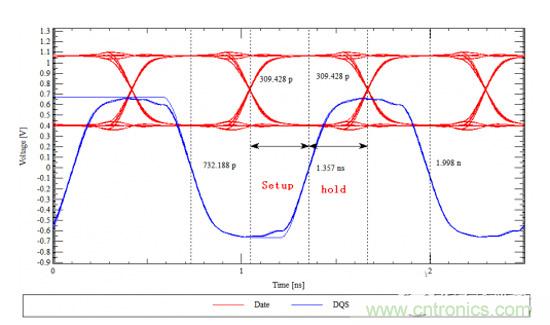

圖8.平移后的眼圖

通過主控芯片的調(diào)節(jié)之后,DQS的邊沿就和DQ信號位的中心對齊了,這樣就能保證數(shù)據(jù)在傳輸?shù)浇邮斩擞凶銐虻慕r間與保持時間。和上面分析時鐘與地址信號一樣,如果DQ與DQS之間等長做的不好,DQS的時鐘邊沿就不會保持在DQ的中間位置,這樣建立時間或者保持時間的裕量就會變小。先簡單的來看一張圖

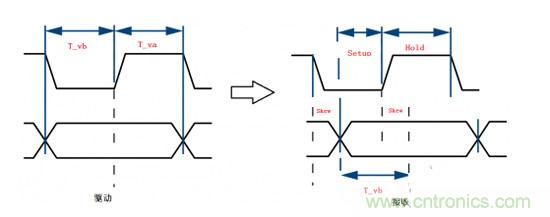

圖9.延時偏差對時序的影響

上圖中,T_vb與T_va表示的是主控芯片在輸出數(shù)據(jù)時時鐘與數(shù)據(jù)之間的時序參數(shù)。在理想情況下,時鐘邊沿和數(shù)據(jù)電平的中心是對齊的,由于時鐘和數(shù)據(jù)傳輸通道不等長,使得時鐘邊沿沒有和數(shù)據(jù)脈沖的中間位置對其,使得建立時間的裕量變小。在理解了這些基礎問題之后,我們需要做的就是將這些時間參數(shù)轉(zhuǎn)化為線長。

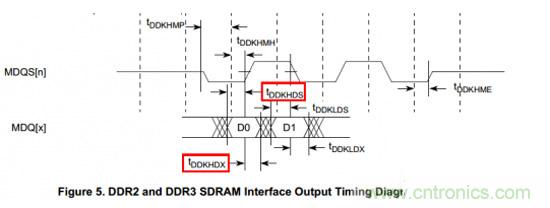

下面我們通過具體實例來看看時序的計算,下圖是Freescale MPC8572 DDR主控芯片手冊,這張圖片定義了從芯片出來的時候,DQS與DQ之間的相位關系。

圖10.MPC8572時序圖

圖11.MPC8572時序參數(shù)

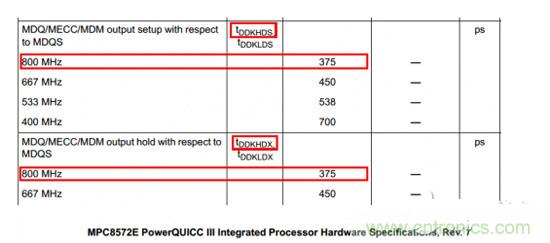

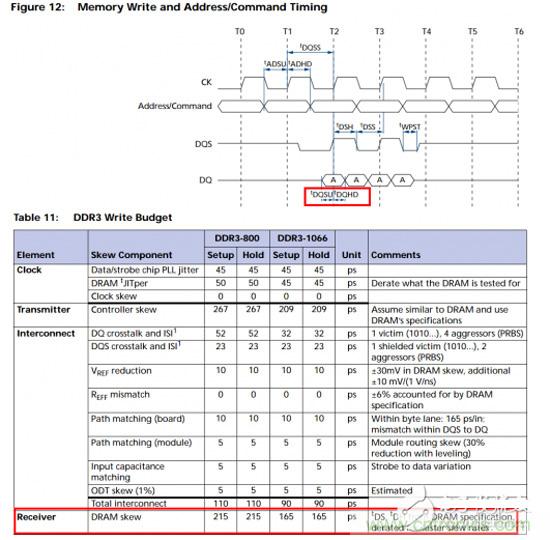

顆粒端為美光DDR,該芯片的時序圖以及時序參數(shù)如下圖所示,這張圖片則定義了顆粒端芯片識別信號所需要的建立時間與保持時間。

圖12.DDR顆粒時序圖以及時序參數(shù)

我們用T_pcbskew來表示DQ與DQS之間的延時偏差,如果想要得到足夠的時序裕量,則延時偏差要滿足以下關系:

T_pcbskew《T_vb-T_setup

T_pcbskew》T_hold-T_va

代入數(shù)據(jù),有:

T_vb-T_setup=375-215=160ps

T_hold-T_va=-160ps

這樣,如果傳輸線的速度按照6mil/ps來計算,T_pcbskew為+/-960mil。大家會發(fā)現(xiàn)裕量很大,當然這只是最理想情況,沒有考慮時鐘抖動以及數(shù)據(jù)信號的抖動,以及串擾、碼間干擾帶來的影響,如果把這些因素都考慮進來,留給我們布線偏差的裕量就比較小了。

綜上所述,時序控制的目的就是要保證數(shù)據(jù)在接收端有充足的建立時間與保持時間,明白了這一點,我們在線長匹配這個問題上就能做到胸有成竹,游刃有余了。