【導(dǎo)讀】逐次逼近型(SAR)ADC是在在工業(yè),汽車,通訊行業(yè)中應(yīng)用最廣泛的ADC之一,例如電機電流采樣,電池電壓電流監(jiān)控,溫度監(jiān)控等等。

通常工程師在設(shè)計SAR ADC時,通常需要注意以下三個方面:ADC前端驅(qū)動設(shè)計,參考電壓設(shè)計,數(shù)字信號輸出部分設(shè)計。本文將介紹ADC的前端驅(qū)動所需要的注意的一些要素。

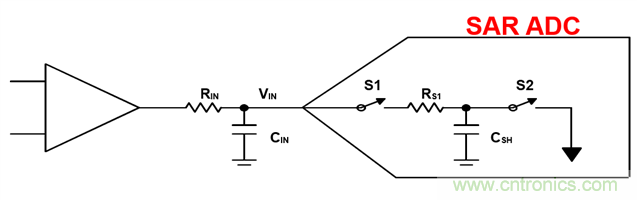

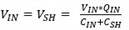

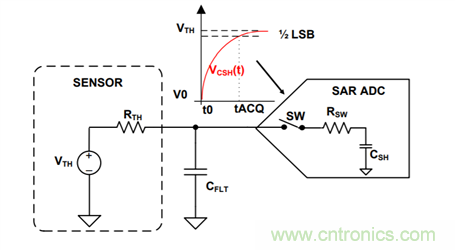

如圖所示是一個常見的SAR ADC的驅(qū)動電路包括驅(qū)動放大器和RC濾波。接下來將從如何設(shè)計RC濾波器,以及如何選擇合適的運算放大器展開。

圖1. SAR ADC驅(qū)動電路基本架構(gòu)

如何設(shè)計RC濾波網(wǎng)絡(luò)

首先我們來看一下RC網(wǎng)絡(luò)的設(shè)置,對于RC網(wǎng)絡(luò),它的主要作用分為以下兩個方面:

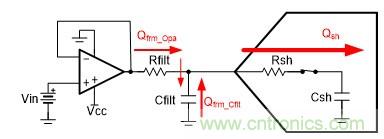

1:對ADC的Csh進行充電,由于ADC采樣保持階段需要輸入給采樣保持電容Csh充電。如圖所示,開始采樣時,Csh的電荷由輸入部分(Qfrm_opa)和RC濾波電容(Qfrm_cflit)提供,保證在一定時間內(nèi)達到精度的要求。顯然,隨著采樣精度和采樣率的不斷提高,驅(qū)動ADC的難度加大,因為必須在有限的時間內(nèi)采樣時間(tacq)內(nèi)將Csh上的電壓達到滿足精度要求(1/2LSB內(nèi))。所以我們在ADC前加入電容,當采樣保持階段時對Csh進行充電,保證采樣的精度。電阻則作為隔離作用,避免運放直接驅(qū)動容性負載,提升系統(tǒng)的穩(wěn)定性。

圖2. SAR ADC采樣保持階段電流方向

2:RC網(wǎng)絡(luò)同時也限制了輸入信號的帶寬,并且降低了運放帶來的噪聲量,但是于此同時,帶寬的限制會使信號的延長建立時間,引起信號的失真

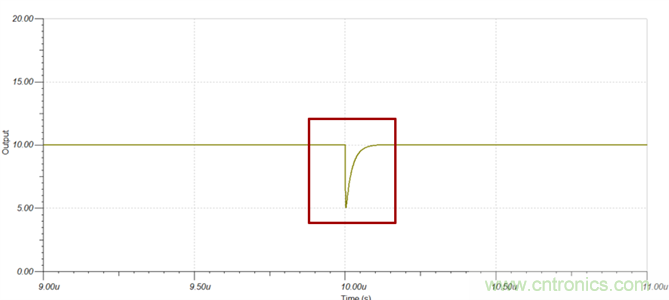

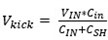

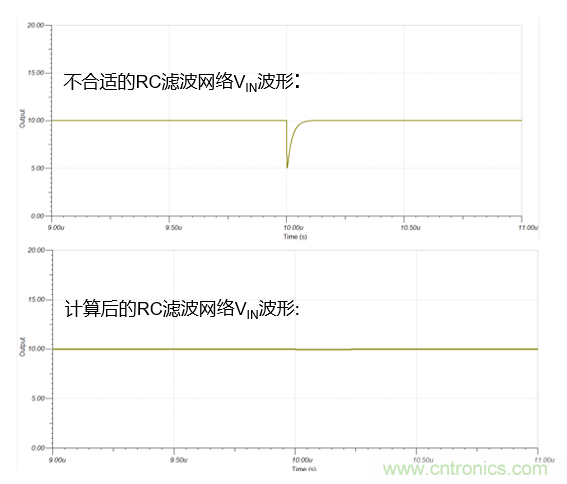

我們設(shè)計RC網(wǎng)絡(luò)的目標就是在有限的時間內(nèi)采樣時間(tacq)內(nèi)將Csh上的電壓達到滿足精度要求(1/2LSB內(nèi)),如果不加入RC或者RC選擇不合適,可能出現(xiàn)如圖所示的情況(橫坐標為時間,縱左邊為Vfilt電壓,可以看到信號幅值變化大且反向恢復(fù)時間長),這是因為運放的帶寬不足或者RC電路中電容太小,導(dǎo)致Qfrm_opa與Qfrm_cflit不能在采樣時間(tacq)內(nèi)將電荷轉(zhuǎn)移至Csh中,如果在信號沒有達到足夠的采樣時間內(nèi)進行采樣,就會產(chǎn)生信號失真。

圖3. 不合適的RC濾波導(dǎo)致信號幅度變化大且反向恢復(fù)時間長

顯然,我們無法同一個RC網(wǎng)絡(luò)使用在不同的SAR ADC的應(yīng)用中,那么我們要怎么去為SAR ADC設(shè)計一個合適的RC濾波網(wǎng)絡(luò)呢?

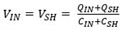

如下圖所示為SAR ADC的簡化原理圖,以最壞的情況,CSH對地放電為例。當開關(guān)S1關(guān)閉時,開關(guān)S2打開時,電容CIN與CSH共享電荷可得出等式 ,由于電容CSH對地放電,則QSH=0,且QIN=VIN*CIN,則可以得出

,由于電容CSH對地放電,則QSH=0,且QIN=VIN*CIN,則可以得出

圖4. SAR ADC驅(qū)動電路基本架構(gòu)

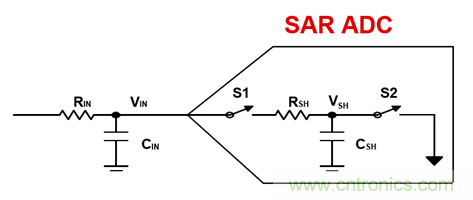

則可以推算出 ,如圖所示:

,如圖所示:

圖5. SAR ADC驅(qū)動VIN電壓

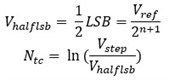

在ADC的采集階段,ADC建立至1/2LSB所需要的RC時間常數(shù) , 其中tacq為采集時間Ntc為建立所需的時間常數(shù)數(shù)目。所需的時間常數(shù)數(shù)目可以通過計算階躍大小VSTEP與建立誤差(本例為1/2LSB)之比的自然對數(shù)來獲得:

, 其中tacq為采集時間Ntc為建立所需的時間常數(shù)數(shù)目。所需的時間常數(shù)數(shù)目可以通過計算階躍大小VSTEP與建立誤差(本例為1/2LSB)之比的自然對數(shù)來獲得:

由此,我們可以求出RC的時間常數(shù) ,根據(jù)

,根據(jù) ,可以得出RC的值以及帶寬。

,可以得出RC的值以及帶寬。

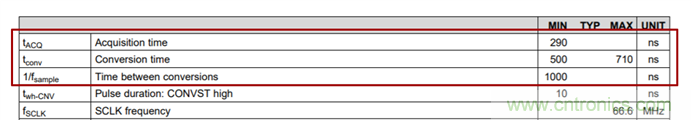

以TI 16位ADC:ADS8860 為例,從數(shù)據(jù)手冊第8頁可以得到以下信息:

圖6. ADS8860數(shù)據(jù)手冊數(shù)據(jù)

它的MAX Conversion time為 710ns ,Min Acquisition time 為290ns ,吞吐率為1Msps,假設(shè),參考電壓為5V,信號為100kHz的正弦波

那么在轉(zhuǎn)換時間,信號最大變化量為:

根據(jù)ADS8860的CSH=59pF,一般CIN選擇CSH的20倍以上,這里取CIN=5.9nF則可以計算出Vkick電壓:

接下來計算建立到1/2LSB的時間常數(shù):

則可以得出:

因此選擇R=8.6ohm,帶寬為3.13MHz

將取值帶入仿真后可得圖,相對于沒有RC濾波的ADC而言,加入合適的RC濾波可以使ADC-Vin電壓變化幅度變小,反向建立時間也更短。

圖7. 不合適的RC與加入計算后RC的VIN電壓波形對比

由我們的公式我們可以知道,當吞吐率越高時,我們對采樣保持的時間就相對越短,從而需要更大的RC帶寬。所以當隨著精度和采樣率的不斷提高,設(shè)計RC的難度會加大,我們需要權(quán)衡設(shè)計驅(qū)動的參數(shù)。

如何選擇適合的驅(qū)動放大器

首先必須說明的是驅(qū)動放大電路并不是總是需要的,他的作用通常有以下幾個:

1. 用于信號類型的轉(zhuǎn)換,例如單端信號轉(zhuǎn)化為差分信號

2. 以對信號進行調(diào)理,例如將信號放大/縮小等

3. 如果輸入阻抗小,可以放置運放來增大輸入的阻抗,和減少輸出阻抗

4. 限制帶寬,防止高頻信號輸入進行干擾

當信號帶寬低,信號變化十分緩慢,如氣體,溫度等,可以直接使用RC進行驅(qū)動,降低成本,結(jié)構(gòu)如圖所示。

圖8. 無運放驅(qū)動SAR ADC電路簡圖

那么在我們選擇運放的時候需要注意以下參數(shù):運放的帶寬,運放的噪聲特性,運放的失真特性等。

運放的帶寬:帶寬大的運放可以讓RC電路更快的進行充電,一般來說,選擇運放的帶寬為RC濾波器的4倍以上,如果需要運放提供電壓增益則需要選擇更大帶寬的運放。但是同時帶寬大的運放往往靜態(tài)電流和失調(diào)/偏置電流會比較大,所以要進行取舍。

運放的噪聲特性:對于運放的噪聲特性來說,為了不讓運放的噪聲對ADC的精度產(chǎn)生影響,一般會使運放的總噪聲在ADC噪聲的1/5左右。如果,ADC的SNR為86dB,Vref=5V,那么該系統(tǒng)中的總噪聲應(yīng)該小于:

根據(jù)計算得出的總噪聲,取ADC噪聲的1/5,進行計算可以計算出應(yīng)該選擇的運放的1/f噪聲和寬帶噪聲的最大影響值,假設(shè)選用的運放有極小的1/f噪聲可以忽略不計的話,可以經(jīng)過以下公式計算,得出結(jié)果:

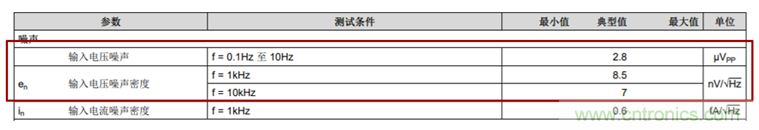

像Ti的產(chǎn)品OPA320,由數(shù)據(jù)手冊第8頁中可得,寬帶噪聲密度為可以滿足要求

圖9. OPA320數(shù)據(jù)手冊噪聲數(shù)據(jù)

運放的失真特性:對于ADC的驅(qū)動運放來說,我們通常需要選擇輸入輸出軌對軌的運放,防止不必要的輸出失真,但是通常正負軌對軌的運放價格相對的高,所以通常使用的是單電源輸入,單極軌對軌的運放。

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請聯(lián)系小編進行處理。

推薦閱讀: