【導讀】在設計階段,由于架構師對電路的功耗要求越來越嚴格,并且倍增系數(shù)越來越大,因此對多路復用級聯(lián)時鐘分頻器的需求也隨之加大。本文分享給大家的是一種采用門控時鐘來設計低功耗時序電路,與傳統(tǒng)電路相比,可支持不同的輸出頻率,同時消耗更低的功耗。

在傳統(tǒng)設計中,所有計算機運算(算法、邏輯和存儲進程)都參考時鐘同步執(zhí)行,時鐘增加了設計中的時序電路數(shù)量。在這個電池供電設備大行其道的移動時代,為了節(jié)省每一毫瓦(mW)的功耗,廠商間展開了殘酷的競爭,因此將電路分成多個電源域并根據(jù)要求關閉它們,并且在設計每個時序電路的同時節(jié)省功耗,這兩點至關重要。時序電路(如計數(shù)器和寄存器)在現(xiàn)代設計中無處不在。本文以約翰遜計數(shù)器為例介紹了如何采用有效門控時鐘來設計高能效的時序電路。

約翰遜計數(shù)器系統(tǒng),可同步提供多種特殊類型的數(shù)據(jù)序列,這對于大多數(shù)重要應用(如D/A轉換器、FSM和時鐘分頻器)來說至關重要。為支持不同頻率(從MHz 到 GHz)的模塊,越來越多的IP集成到片上系統(tǒng),因此,設計中在不同層級實施了許多可支持多個分頻因子的時鐘分頻器。本文中,我們介紹了一款節(jié)能設計,即用帶有門控時鐘的多級可編程約翰遜計數(shù)器系統(tǒng)來取代多個時鐘分頻器,該計數(shù)器可提供8至任何偶數(shù)值(在本文中為38)的時鐘分頻因子。下面,我們將探討實施細節(jié)和該技術的優(yōu)劣。

典型時序電路

圖1給出的是一款傳統(tǒng)4位上升沿約翰遜計數(shù)器。約翰遜計數(shù)器只不過是修改過的移位寄存器,其最后一個D觸發(fā)器的反相輸出作為第一個D觸發(fā)器的輸入。所有其他觸發(fā)器將接收上一個觸發(fā)器所提供的輸出。

圖1:傳統(tǒng)約翰遜計數(shù)器。

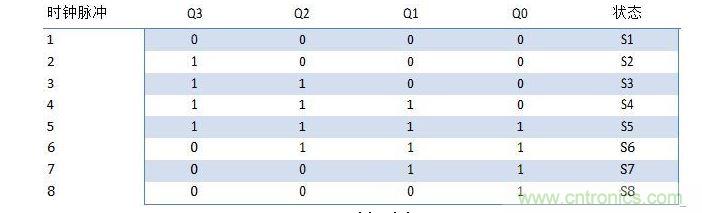

如表1所示,在所有的縱列中,4個連續(xù)的“0”后面都跟隨著4個連續(xù)的“1”,但所有縱列都位于不同的階段。約翰遜計數(shù)器可同步創(chuàng)建一個特定的數(shù)據(jù)模式。該數(shù)據(jù)模式在建模時非常有用,因為它可以使用任何抽頭就可以產(chǎn)生一個有不同階段的時鐘樣式的模式。此外,從表中可以推導出,約翰遜計數(shù)器只使用了N個觸發(fā)器提供2N個狀態(tài),因此,與標準環(huán)形計數(shù)器相比,約翰遜計數(shù)器僅需要一半數(shù)量的觸發(fā)器便可實現(xiàn)同樣的MOD。

表1:約翰遜計數(shù)器的狀態(tài)表。

[page]

典型時序電路的缺陷

如圖1所示,這種電路最大的缺點是不可配置,因此,不能改變時鐘分頻因子。一個N觸發(fā)器設計只能產(chǎn)生2N個周期的時鐘。需要預先將固定數(shù)量的觸發(fā)器加入到設計中,才能產(chǎn)生固定周期的時鐘。這大大阻礙了特定時鐘的設計,而且多個這樣的設計,需要多種分頻因子來進行分頻。

另外,該設計非常耗能,并且也沒有機制可通過高效門控時鐘來節(jié)省動態(tài)功耗。如表1所示,Q3只能在時鐘脈沖2和時鐘脈沖6中改變其輸出,對于所有其他時鐘而言,觸發(fā)器一次又一次地存儲了相同的數(shù)據(jù)。這導致在時鐘周期內(nèi)產(chǎn)生了不必要的功耗,而采用適合的門控時鐘可解決該問題。

通過調(diào)整結構和門控時鐘來增強電路

任何時序電路都可通過調(diào)整結構和有效的門控時鐘加以增強。圖1中所示的約翰遜計數(shù)器在圖2種得到了增強,可以靈活地支持多種分頻因子,產(chǎn)生可變化的輸出頻率。

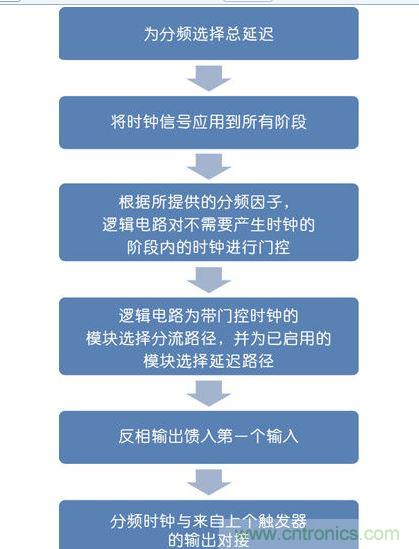

為了使其可編程,觸發(fā)器的多個延遲階段都加入了所需的組合邏輯,以根據(jù)所需分頻因子進行選擇。

圖2顯示的就是一款低功耗可編程約翰遜計數(shù)器。該電路包括級聯(lián)延遲階段B1、B2、B3、B4、逆變器I、參考時鐘輸入CLK、門控時鐘邏輯CGL,以及控制邏輯(分頻器和減法器),可根據(jù)要求選擇觸發(fā)器組合。

圖2:低功耗多級可編程約翰遜計數(shù)器。

在圖2所示的修改后的約翰遜計數(shù)器電路中,我們采用了19個D觸發(fā)器,這些觸發(fā)器提供8至38以內(nèi)的偶數(shù)值的分頻因子??赏ㄟ^添加額外的觸發(fā)器和多路復用器,使所需分頻因子進一步增加至任何偶數(shù)值。多個路徑可將觸發(fā)器 “a、j、o和r” 的輸出連接至相應的多路復用器輸入,例如,分流路徑將觸發(fā)器 “a”的輸出連接至第一個多路復用器的第一個輸入,延遲路徑則將觸發(fā)器“a”的輸出[經(jīng)過一組觸發(fā)器(b、c、d、e、f、g、h、i)]連接至第一個多路復用器的第二個輸入。這種實施方案允許選擇多路復用器輸出,使電路具備所需的可配置性,可以支持多個分頻因子。

如圖3所示,為了節(jié)省功耗,控制電路輸出饋入CGL中,以根據(jù)所需分頻因子啟用或禁用“延遲路徑觸發(fā)器”的時鐘。當分頻因子為2N時,需要N個觸發(fā)器提供所需的時鐘頻率。為了促進多路復用器輸入的選擇,并為時鐘門控邏輯啟用所選的輸入,我們添加了一個主要由減法器構成的控制邏輯。該減法器可根據(jù)用戶所提供的分頻因子,將N-4作為輸出提供,并且減法器(sel[3:0])的二進制輸出位數(shù)每個都可作為4個多路復用器(1st、2nd、3rd、4th)的相應選擇線路,并使CGL以高效的方式對觸發(fā)器的時鐘進行門控。

這有效地實現(xiàn)了設計的可編程化,并降低了計數(shù)器的動態(tài)功耗。

圖3:電路運算說明圖。

電路運算

以分頻因子為10(即2N=10)的電路為例。由于傳統(tǒng)約翰遜計數(shù)器在分頻因子為2N時需要N個觸發(fā)器,要使分頻因子為10,電路中需要2N/2 = 10/2 = 5個觸發(fā)器。分頻器電路的輸出是2N/2 = 5,這時減法器的輸出則為(5-4) = 1,再饋入多路復用器的選擇線路,其二進制表示為0001。這個4位sel[3:0]=0001信號極為重要,因為它不僅控制著門控時鐘邏輯,還在分流和延遲路徑中做出選擇。

圖4:分頻因子為10的電路運算。

在這種情況下,只有Sel[0]會變?yōu)?并啟用s觸發(fā)器的時鐘,并且同樣地,sel[3]、sel[2]、sel[1]將相應禁用 (b、c、d、e、f、g、h、i)、(k, l, m, n)、(p、q)觸發(fā)器的時鐘,見圖4中突顯部分。另外需要注意的是,“a, j, o 和r”觸發(fā)器將始終啟用。這樣一來,不僅啟用了所需的觸發(fā)器,并且該電路可在第4個多路復用器的輸出上獲得所需的輸出時鐘。因此,在這個示例中,共有5個觸發(fā)器接收到時鐘,其他觸發(fā)器的時鐘將自動被禁用。

我們對上述計數(shù)器進行了模擬,其結果以RTL波形的形式呈現(xiàn)在圖5中。根據(jù)圖5可以推出:修改后的計數(shù)器采用sel[3:0]作為4’h0001,將一個100 MHz的時鐘進行分頻,提供10 MHz的輸出。

圖5:分頻因子為10的波形。

推薦的電路可實現(xiàn)各種組合,表2列出了多路復用器所選擇的輸入。

表2:不同分頻因子的多路復用器和CGIC的選擇邏輯。

推薦方法的優(yōu)勢

本文所介紹的約翰遜計數(shù)器可根據(jù)分頻因子(范圍為8至38)進行編程,按提供給計數(shù)器組合邏輯的輸入所配置的提供一系列輸出頻率。

即使此計數(shù)器中配備了額外的硬件來實現(xiàn)可編程性,但是該電路的功耗通過一個邏輯提供的有效門控時鐘進行控制,該邏輯與在選擇階段挑選多路復用器時所采用的邏輯相同,并啟用門控時鐘單元。

因此,將門控時鐘添加到設計內(nèi)以后,任何從移位寄存器傳送至計數(shù)器的時序邏輯都可以變得更加高效,并且片上系統(tǒng)的一系列此類電路綜合起來可以節(jié)省功耗并延長設備電池壽命。

總結

在設計階段,由于架構師對電路的功耗要求越來越嚴格,并且倍增系數(shù)越來越大,因此對多路復用級聯(lián)時鐘分頻器的需求也隨之加大,但這種分頻器會使電路消耗更多的功耗,并且占用更大的芯片面積。結構調(diào)整后的設計卻提供了一個更加輕松的解決方案,與傳統(tǒng)電路相比,重組后的電路可支持不同的輸出頻率,同時消耗更低的功耗。該解決方案還可輕松應用至各種其他設計中,使其他設計變得更加節(jié)能。