【導(dǎo)讀】FinFET晶體管與平面器件相比����,它們可以提供更低的功耗、更高的性能和更小的面積���。這使得FinFET對(duì)智能手機(jī)���、平板電腦及要求長(zhǎng)電池壽命和高性能的其他產(chǎn)品來(lái)說(shuō)極具吸引力�。那這是不是就說(shuō)明他是完美的呢����?答案是否定的。

現(xiàn)在主要的代工廠都在生產(chǎn)FinFET晶體管���,這些FinFET以創(chuàng)紀(jì)錄的速度實(shí)現(xiàn)了從設(shè)計(jì)到現(xiàn)貨產(chǎn)品的轉(zhuǎn)變�。FinFET的發(fā)展普及一直都比較穩(wěn)定����,因?yàn)榕c平面器件相比,它們可以提供更低的功耗���、更高的性能和更小的面積����。這使得FinFET對(duì)智能手機(jī)����、平板電腦及要求長(zhǎng)電池壽命和高性能的其他產(chǎn)品來(lái)說(shuō)極具吸引力。

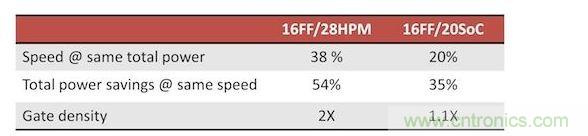

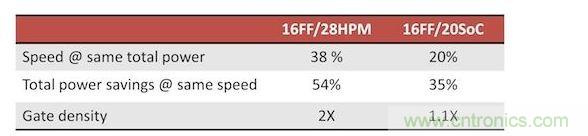

當(dāng)Intel首次在22nm節(jié)點(diǎn)使用FinFET時(shí),他們聲稱與bulk�����、PDSOI或FDSOI相比�����,F(xiàn)inFET在相同的總功耗條件下性能高出37%����,或者在相同速度條件下功耗低50%����。這些數(shù)據(jù)非常有吸引力,而且在向14nm及更小工藝節(jié)點(diǎn)發(fā)展時(shí)還有進(jìn)一步改進(jìn)的空間�。

圖1. FinFET的性能�,功耗和面積優(yōu)勢(shì)

在使用功耗方面,控制功率泄漏對(duì)于平面器件�����,特別是在較小的節(jié)點(diǎn)來(lái)說(shuō)���,已然成為了一項(xiàng)艱巨挑戰(zhàn)�����。通過(guò)抬升溝道���,包裹溝道四周的柵極�����,F(xiàn)inFET可以創(chuàng)建一種完全耗盡型溝道����,從而克服平面晶體管的漏電流問(wèn)題���。FinFET所具有的更好的溝道控制能力可以用來(lái)實(shí)現(xiàn)更低的閾值和供電電壓�����。

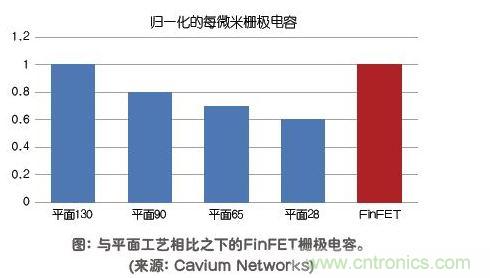

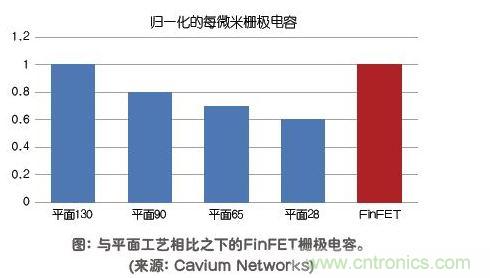

雖然漏電流在FinFET中是受控的�,但動(dòng)態(tài)功耗占總功耗的很大部分���。與平面晶體管相比����,F(xiàn)inFET具有更大的引腳電容,因而會(huì)導(dǎo)致更高的動(dòng)態(tài)功耗值����。據(jù)CaviumNetworks描述,“與28nm工藝相比����,F(xiàn)inFET的每微米柵極電容提高了66%,與130nm平面節(jié)點(diǎn)的水平相當(dāng)����。”平面器件和FinFET器件的柵極電容值比較如圖所示����。

圖2:與平面工藝相比之下的FinFET柵極電容。

那么這對(duì)設(shè)計(jì)工程師來(lái)說(shuō)意味著什么呢����?從實(shí)現(xiàn)角度看又會(huì)對(duì)設(shè)計(jì)流程造成怎樣的改變?動(dòng)態(tài)功耗(也稱為開(kāi)關(guān)功耗)在優(yōu)化過(guò)程中應(yīng)成為一個(gè)代價(jià)函數(shù)����,必須在流程的所有階段加以充分考慮。

FinFET增加了物理設(shè)計(jì)流程的復(fù)雜性。更嚴(yán)格的設(shè)計(jì)規(guī)則和FinFET工藝要求(比如具有電壓閾值意識(shí)的間距設(shè)計(jì)����、植入層規(guī)則等),都將對(duì)綜合����、布局、底層規(guī)劃和優(yōu)化引擎施加約束����,從而直接影響設(shè)計(jì)的指標(biāo)。同時(shí)由于FinFET是在16nm/14nm工藝實(shí)現(xiàn)����,多重圖案技術(shù)將自動(dòng)成為使用FinFET的任何設(shè)計(jì)的一部分,這又增加了另一層的復(fù)雜性����。

針對(duì)FinFET的設(shè)計(jì)自動(dòng)化技術(shù)需要具有FinFET意識(shí),以降低開(kāi)關(guān)功耗����,并提供具有功耗意識(shí)的RTL綜合、活動(dòng)驅(qū)動(dòng)型布局和優(yōu)化����、時(shí)鐘樹(shù)綜合(CTS)功耗降低以及并行優(yōu)化動(dòng)態(tài)與泄漏等功能����。功耗優(yōu)化需要從設(shè)計(jì)流程的早期開(kāi)始����,架構(gòu)選擇需要具有功耗友好特性,以便確保設(shè)計(jì)在實(shí)現(xiàn)時(shí)具有最低的功耗����。

數(shù)字實(shí)現(xiàn)過(guò)程是從RTL綜合開(kāi)始的。由于FinFET被應(yīng)用于最新����、最大的設(shè)計(jì)����,RTL綜合引擎必須擁有在合理運(yùn)行時(shí)間處理1億個(gè)以上門電路的能力。當(dāng)然����,它還必須提供高質(zhì)量的結(jié)果,這可以在考慮芯片的所有因素后在全芯片級(jí)執(zhí)行RTL綜合來(lái)實(shí)現(xiàn)����。執(zhí)行多個(gè)具有不同設(shè)計(jì)約束條件的綜合任務(wù)來(lái)探索不同設(shè)計(jì)方案也是很有用的����。能夠觀察設(shè)計(jì)指標(biāo)如何相互影響有助于在滿足功耗����、性能和面積指標(biāo)要求方面做出聰明的折中方案����。

為了滿足功耗目標(biāo),實(shí)現(xiàn)流程需要從綜合開(kāi)始并貫穿整個(gè)物理設(shè)計(jì)流程����,采取一系列的降功耗策略。最常見(jiàn)的策略包括多閾值庫(kù)����、時(shí)鐘選通、多角落/多模式(MCMM)功耗優(yōu)化����、引腳交換、寄存器集中����、重映射和功率密度驅(qū)動(dòng)型布局����。RTL級(jí)功耗分析對(duì)于分析和修復(fù)設(shè)計(jì)流程早期出現(xiàn)的功耗問(wèn)題來(lái)說(shuō)非常重要����。

在RTL和版圖之間交叉檢測(cè)的能力也有助于在設(shè)計(jì)流程早期識(shí)別和調(diào)試問(wèn)題,并最大限度地減小最后一刻才發(fā)現(xiàn)問(wèn)題的概率����。

在先進(jìn)節(jié)點(diǎn)使用FinFET的設(shè)計(jì)實(shí)現(xiàn)工具必須在與各家代工廠的緊密合作下得到增強(qiáng)和更新。在代工廠����、EDA公司和雙方客戶之間要開(kāi)展大量的工程技術(shù)合作,以便芯片設(shè)計(jì)人員能夠充分發(fā)揮每種新工藝節(jié)點(diǎn)的優(yōu)勢(shì)����。