【導讀】在上次的推文《泛林小課堂 | 半導體制造八大步驟(上篇)》中,我們給大家介紹了晶圓加工、氧化和光刻三大步驟。本期,我們將繼續(xù)探索半導體制造過程中的兩大關鍵步驟:刻蝕和薄膜沉積。

第四步 · 刻蝕

在晶圓上完成電路圖的光刻后,就要用刻蝕工藝來去除任何多余的氧化膜且只留下半導體電路圖。要做到這一點需要利用液體、氣體或等離子體來去除選定的多余部分。

刻蝕的方法主要分為兩種,取決于所使用的物質:使用特定的化學溶液進行化學反應來去除氧化膜的濕法刻蝕,以及使用氣體或等離子體的干法刻蝕。

濕法刻蝕

使用化學溶液去除氧化膜的濕法刻蝕具有成本低、刻蝕速度快和生產率高的優(yōu)勢。然而,濕法刻蝕具有各向同性的特點,即其速度在任何方向上都是相同的。這會導致掩膜(或敏感膜)與刻蝕后的氧化膜不能完全對齊,因此很難處理非常精細的電路圖。

干法刻蝕

干法刻蝕可分為三種不同類型。第一種為化學刻蝕,其使用的是刻蝕氣體(主要是氟化氫)。和濕法刻蝕一樣,這種方法也是各向同性的,這意味著它也不適合用于精細的刻蝕。

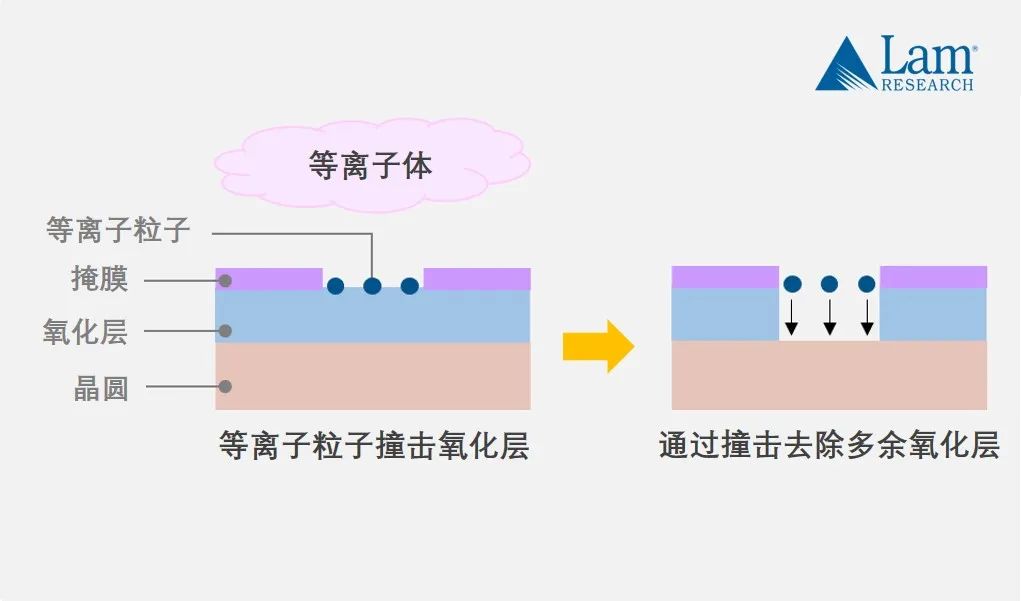

第二種方法是物理濺射,即用等離子體中的離子來撞擊并去除多余的氧化層。作為一種各向異性的刻蝕方法,濺射刻蝕在水平和垂直方向的刻蝕速度是不同的,因此它的精細度也要超過化學刻蝕。但這種方法的缺點是刻蝕速度較慢,因為它完全依賴于離子碰撞引起的物理反應。

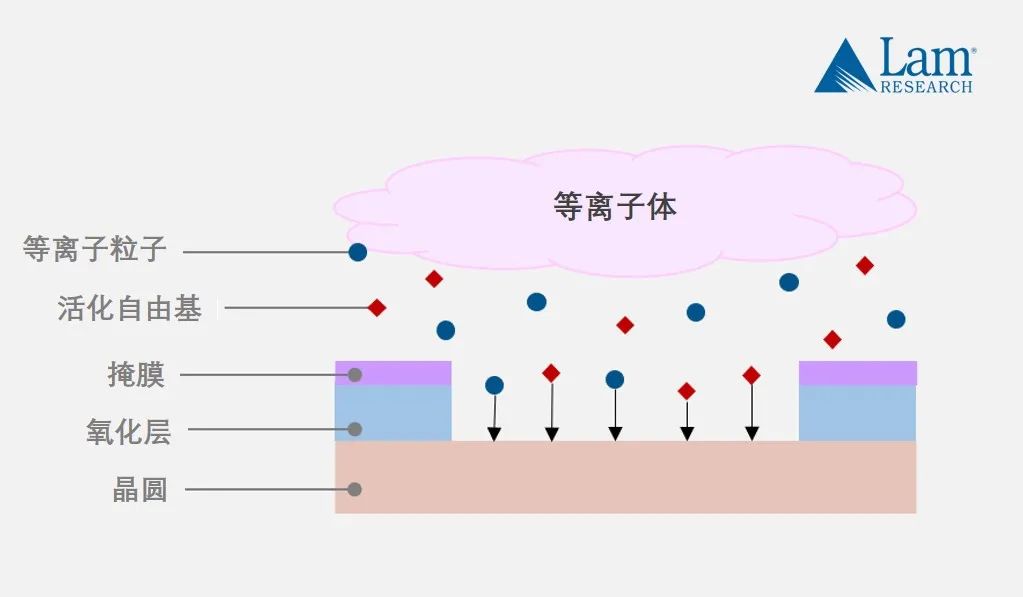

最后的第三種方法就是反應離子刻蝕(RIE)。RIE結合了前兩種方法,即在利用等離子體進行電離物理刻蝕的同時,借助等離子體活化后產生的自由基進行化學刻蝕。除了刻蝕速度超過前兩種方法以外,RIE可以利用離子各向異性的特性,實現(xiàn)高精細度圖案的刻蝕。

如今干法刻蝕已經(jīng)被廣泛使用,以提高精細半導體電路的良率。保持全晶圓刻蝕的均勻性并提高刻蝕速度至關重要,當今最先進的干法刻蝕設備正在以更高的性能,支持最為先進的邏輯和存儲芯片的生產。

針對不同的刻蝕應用,泛林集團提供多個刻蝕產品系列,包括用于深硅刻蝕的DSiE™系列和Syndion®系列、關鍵介電刻蝕產品Flex®系列、用于導體刻蝕的Kiyo®系列、用于金屬刻蝕的Versys® Metal系列。在行業(yè)領先的Kiyo和Flex工藝模塊的基礎上,泛林集團還于去年3月推出Sense.i®系列,其高性能表現(xiàn)能夠滿足前述生產過程所需的精確性和一致性要求,適合各種關鍵和半關鍵性刻蝕應用。

第五步 · 薄膜沉積

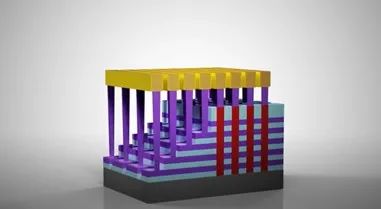

為了創(chuàng)建芯片內部的微型器件,我們需要不斷地沉積一層層的薄膜并通過刻蝕去除掉其中多余的部分,另外還要添加一些材料將不同的器件分離開來。每個晶體管或存儲單元就是通過上述過程一步步構建起來的。我們這里所說的“薄膜”是指厚度小于1微米(μm,百萬分之一米)、無法通過普通機械加工方法制造出來的“膜”。將包含所需分子或原子單元的薄膜放到晶圓上的過程就是“沉積”。

要形成多層的半導體結構,我們需要先制造器件疊層,即在晶圓表面交替堆疊多層薄金屬(導電)膜和介電(絕緣)膜,之后再通過重復刻蝕工藝去除多余部分并形成三維結構。可用于沉積過程的技術包括化學氣相沉積 (CVD)、原子層沉積 (ALD) 和物理氣相沉積 (PVD),采用這些技術的方法又可以分為干法和濕法沉積兩種。

01 化學氣相沉積

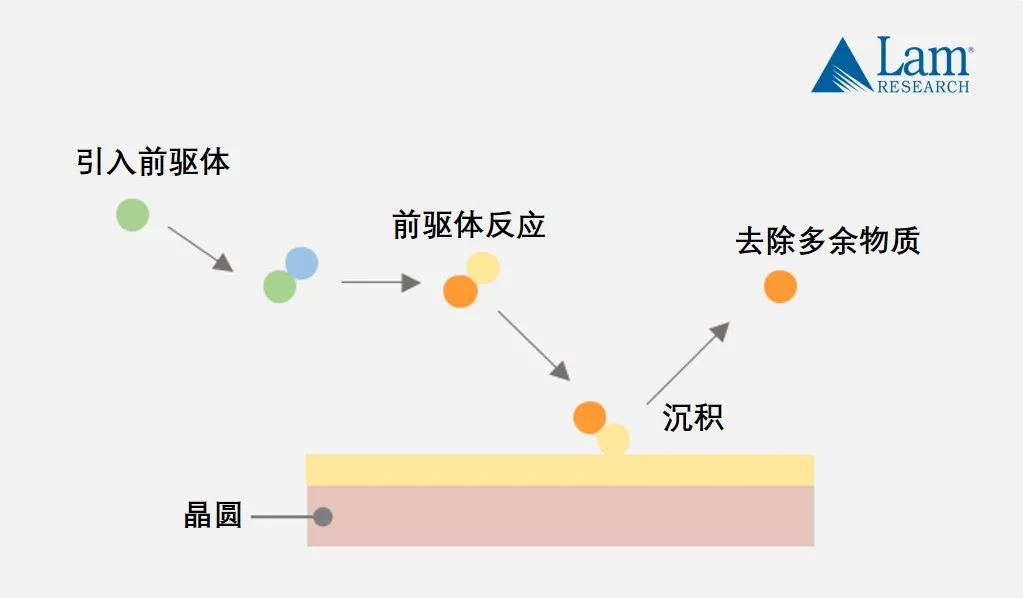

在化學氣相沉積中,前驅氣體會在反應腔發(fā)生化學反應并生成附著在晶圓表面的薄膜以及被抽出腔室的副產物。

等離子體增強化學氣相沉積則需要借助等離子體產生反應氣體。這種方法降低了反應溫度,因此非常適合對溫度敏感的結構。使用等離子體還可以減少沉積次數(shù),往往可以帶來更高質量的薄膜。

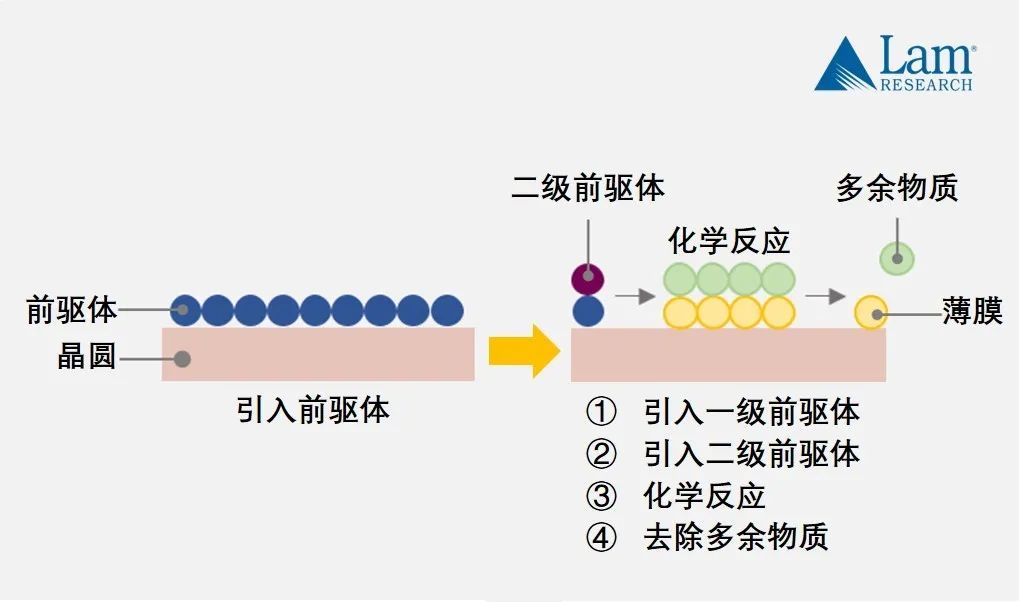

02 原子層沉積

原子層沉積通過每次只沉積幾個原子層從而形成薄膜。該方法的關鍵在于循環(huán)按一定順序進行的獨立步驟并保持良好的控制。在晶圓表面涂覆前驅體是第一步,之后引入不同的氣體與前驅體反應即可在晶圓表面形成所需的物質。

03 物理氣相沉積

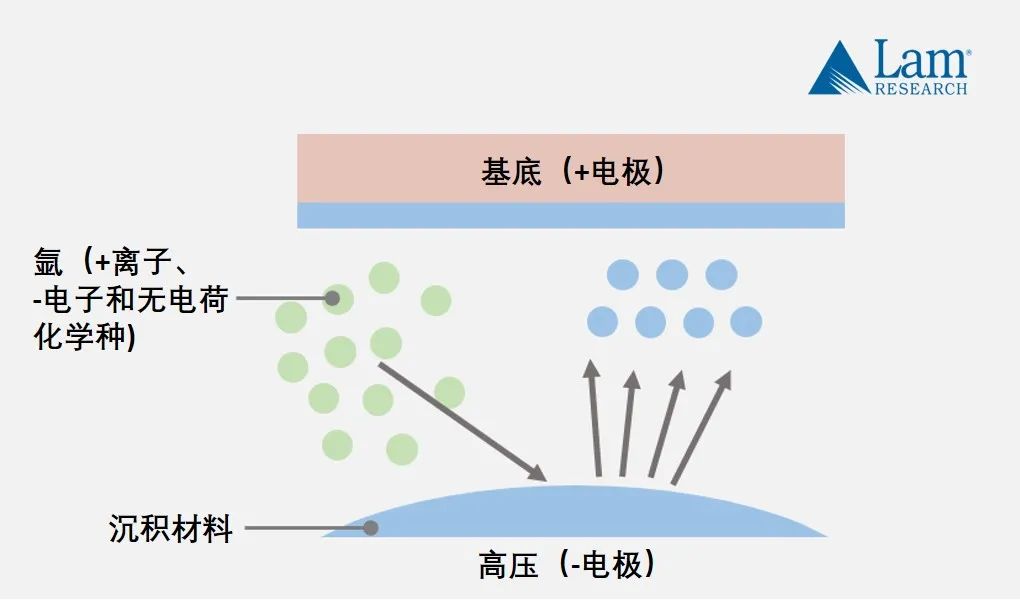

顧名思義,物理氣相沉積是指通過物理手段形成薄膜。濺射就是一種物理氣相沉積方法,其原理是通過氬等離子體的轟擊讓靶材的原子濺射出來并沉積在晶圓表面形成薄膜。

在某些情況下,可以通過紫外線熱處理 (UVTP) 等技術對沉積膜進行處理并改善其性能。

泛林集團的沉積設備均具備出色的精度、性能和靈活性,包括適用于鎢金屬化工藝的ALTUS®系列、具有后薄膜沉積處理能力的SOLA®系列、高密度等離子體化學氣相沉積SPEED®系列、采用先進ALD技術的Striker®系列以及VECTOR® PECVD系列等。

下一期,我們將為大家介紹半導體制造中的最后三個重要步驟——互連、測試和封裝,敬請期待!

來源:泛林半導體設備技術

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯(lián)系小編進行處理。

推薦閱讀: