【導(dǎo)讀】當(dāng)你設(shè)計電源網(wǎng)絡(luò)時,得考慮它們對電路設(shè)計的影響,并為其優(yōu)化布線,否則就無法獲得所有制程微縮的優(yōu)勢,本文就主要講解應(yīng)對芯片設(shè)計復(fù)雜性,EDA工具如何做到新典范設(shè)計。

在近日于美國舉行之年度國際固態(tài)電路會議(InternaTIonal Solid State Circuits Conference,ISSCC)的一場專題演說中,臺積電設(shè)計暨技術(shù)平臺副總經(jīng)理侯永清(Cliff Hou)表示,工程師需要能因應(yīng)今日芯片設(shè)計復(fù)雜性的新工具;而他也指出,針對四個目前的主要市場,需要采用包括機(jī)器學(xué)習(xí)在內(nèi)之新技術(shù)、新假設(shè)的個別工具。

「我們需要一種新的設(shè)計典范(paradigm)來克服芯片設(shè)計挑戰(zhàn);」侯永清指出:「我們是時候該推進(jìn)設(shè)計典范,我們一直只涵蓋設(shè)計領(lǐng)域的一小部份?!顾硎?,產(chǎn)業(yè)界在過去十年是由行動應(yīng)用所驅(qū)動,圍繞著智能型手機(jī)SoC建立設(shè)計數(shù)據(jù)庫:「現(xiàn)在我們了解,行動應(yīng)用可以做為一個起點,但我們需要為汽車、高性能系統(tǒng)以及物聯(lián)網(wǎng)(IoT)等設(shè)計考慮大不相同的應(yīng)用,優(yōu)化電路設(shè)計?!?/div>

侯永清展示了臺積電針對一系列手機(jī)與可穿戴式裝置設(shè)計應(yīng)用的四種不同SRAM設(shè)計,他也在專題演說中列出臺積電已經(jīng)看到某些進(jìn)展的棘手挑戰(zhàn);舉例來說,從40奈米到7奈米節(jié)點,金屬層的電阻增加一倍,而臺積電已經(jīng)在導(dǎo)線下打造了復(fù)雜的通孔柱(via pillars)堆棧,但并不能完全減輕這個問題。

臺積電還根據(jù)芯片是否需要更高的密度或速度,采用了兩種金屬;侯永清表示,那些選項:「需要設(shè)計變革以及EDA強(qiáng)化…EDA供貨商們已經(jīng)意識到這些問題,初步解決方案看來頗具前景?!勾送?,電源網(wǎng)絡(luò)的建構(gòu)也必須非常小心,以避免在晶體管密度增加時的單元利用率(cell uTIlizaTIon)下降;他描述了能讓單元利用率在7奈米節(jié)點由大約74%回升到79%的進(jìn)展。

「當(dāng)你設(shè)計電源網(wǎng)絡(luò)時,得考慮它們對電路設(shè)計的影響,并為其優(yōu)化布線,否則就無法獲得所有制程微縮的優(yōu)勢;」侯永清還展示了能因應(yīng)隨著設(shè)計轉(zhuǎn)移到更低電壓供電水平而增加之延遲變異(delay variaTIon)的新技術(shù),他并呼吁催生精細(xì)度更高的新一代設(shè)計編譯程序,以優(yōu)化特定領(lǐng)域與性能需求。

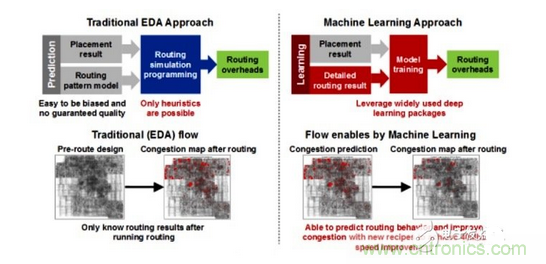

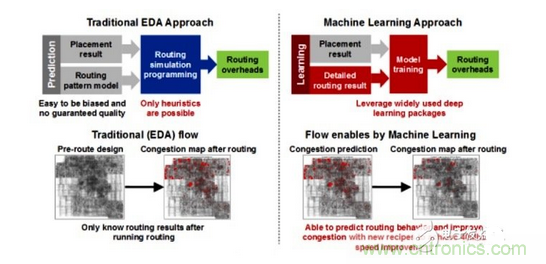

臺積電利用機(jī)器學(xué)習(xí)在芯片設(shè)計繞線前預(yù)測線路擁擠,讓速度增加了40MHz(來源:ISSCC)

最后他展示了兩個將機(jī)器學(xué)習(xí)應(yīng)用于芯片設(shè)計的案例,其中之一是在芯片布線之前,運(yùn)用預(yù)測線路擁擠(congestion)的模型,將芯片速度提升40MHz。另一個案例則是能產(chǎn)生2萬個頻率閘控單元(clock gating cell)的先進(jìn)設(shè)計,因為規(guī)模太大,設(shè)計工程師會被迫采取全局約束(global constraint);侯永清展示了一個機(jī)器學(xué)習(xí)模型,能預(yù)測單元中的延遲并設(shè)定其個別限制。